# A High-Voltage Generator and Multiplexer for Electrostatic Actuation in Programmable Matter

Yimai Peng, Student Member, IEEE, Gordy Carichner, Member, IEEE, Yejoong Kim, Li-Yu Chen, Rémy Tribhout, Benoît Piranda, Julien Bourgeois, David Blaauw, Fellow, IEEE, Dennis Sylvester, Fellow, IEEE

Abstract-Programmable matter (PM) consists of tiny, mmscale quasi-spherical robots that can be combined and programmed to form any arbitrary 3-D shape autonomously. While PM enables instant structural visualization and opens up a host of industrial and artistic applications, it also raises significant challenges in micro-robot control, communication and actuation that are difficult to support with existing systemon-chip (SoC) designs. This paper presents a high-voltagegeneration-and-multiplexer (HVGM) chip specially designed for electrostatic actuation of micro-robots for applications such as PM. The HVGM individually controls 12 pairs of +/- electrodes using a positive and negative charge pump and mux-structure, consuming only 286nW power when switching a 10pF electrode at 155V/s, and producing a differential voltage of 103V (29× voltage gain from 3.6V) in measurement. We also show a complete microsystem of stacked dies, measuring 3×1.4×1.1 mm, including the HVGM, a processor, radio, and harvester that achieves energyautonomous operation, and can be integrated into a micro-robot "Catom" via a flexible PCB.

*Index Terms*—Programmable Matter, Micro-robotics, Electrostatic actuation, High-voltage generator, Voltage multiplexer, Low-power circuit, Chip stack system.

## I. INTRODUCTION

THE concept of programmable matter (PM), defined as matter that can change its physical properties based on a user's input, has been pursued for a long time to achieve the ultimate vision of achieving a universal meta-material for use in daily lives. Improved 3D printing and VLSI/MEMS technology have enabled the realization of PM with millimeter-sized intelligent micro-robots [1]. PM consists of tiny, mm-scale quasi-spherical robots called Catoms, which can autonomously attach themselves in different positions to their neighbors using electrostatic forces. When different Catoms make surface contact, the difference in their surface potentials creates an electrostatic force, bonding them together (latching) or causing a rotation/movement (actuation). By combining thousands of Catoms, a morphable 3D structure can be programmed to take arbitrary shapes. The PM hardware structure can also be manipulated and changed externally while the resulting changes are tracked and captured using sensors inside each Catom and synchronized with a simulation/3-D model inside the software environment. Conversely, we can also modify the 3-D model through the software, and the Catoms will be actuated to reform the PM shape and reflect the change. This 2-way interaction induces a scalable, real-time, efficient, and expressive way of implementing a virtual reality. At the same time it creates an ensemble of micro-robots, which can interact with other communicating things through the IoT.

The realization of PM requires a sophisticated system design, including geometry design, control algorithms, simulation, software-hardware co-design and industrial design [2]-[5]. In this paper we show for the first time a micro-controller design that resides in the Catom and supports its communication, computation, actuation and power management for autonomous operation. While introducing the complete micro-controller system using a chip stack, we focus on the chip layer that is related to actuation of the PM.

A key point to actuation in PM (and other micro-robotic applications) is the generation and control of high voltages (e.g., 100V) at the Catom surfaces (insulators). When different Catoms make surface contact, the difference in their surface potentials will create an electrostatic force, bonding them together (latching) or causing a rotation/movement (actuation). Prior on-chip high voltage generators [6]-[12] are capable of providing sufficient voltage levels for actuation, but their application is greatly limited due to the remaining challenges:

- The high-voltage generation chip should be smaller than a few mm to be contained inside the Catom, ensuring that the whole Catom is light weight. This precludes the use of bulky off-chip components such as inductors and discrete capacitors, which are commonly used by boost converters [13]-[16].

- To allow different actuation patterns of a Catom, the high-voltage chip needs to support all 12 Catom surfaces with individual voltage control.

- Given the small Catom size, energy resources (e.g., a tiny battery) are greatly limited inside the Catom. The high-voltage generation chip must consume sub-µW power to ensure system lifetime.

- 4) The Catom surface electrodes present only capacitive loads to the chip without DC current. Furthermore, the PM actuation frequency is low (less than 100Hz), resulting in a low (nW level) reactive power. This makes it challenging to achieve high energy efficiency because the circuit power overhead (clock generation, switching loss, leakage) is not amortized over a large output current.

To address these challenges, this paper presents a new driving chip referred to as a High-voltage-generator-and-multiplexer (HVGM) [17] for Catom actuation and other capacitive MEMS actuators. The HVGM consists of a single pump with 12 novel high-voltage multiplexer circuits that enable individual control for each electrode output voltage, amortizing area and switching overhead/leakage. Also, since

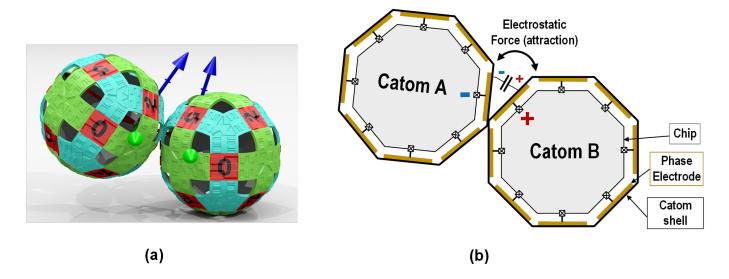

Fig. 1. Geometrical design of a Quasi-Spherical Module (Catom) for Building Programmable Matter [2].

a)

Fig. 2. (a) The actuation (rotation) operation shown in [1] and (b) the 2-D diagram showing the electrostatic attraction force generation in this work.

the multiplexers can turn electrodes off (0V) while keeping the pump active, we avoid discharge and recharge of flying pump capacitors, further saving significant energy. Implemented in a 70V process, we obtain a greater than 100V differential potential across an electrode pair with programmable voltage scale and slew rate at sub- $\mu$ W power levels.

The remainder of this paper is organized as follows. Section II presents the Catom micro-controller design, which we show for the first time, emphasizing the actuation of the Catom and the single pump topology of the HVGM. Section III describes the implementation of HVGM in detail, including the design of high-voltage multiplexers for high voltages in positive and negative domains. Section IV shows the measurement of the HVGM, with the current progress on the Catom integration and testing. Section V draws conclusions.

# II. PROGRAMMABLE MATTER WITH ELECTROSTATIC ACTUATION

## A. Catom Design with Electrostatic Actuation

The building block for PM is a quasi-spherical module called a Catom, proposed in [1], that consists of 12 numbered square surfaces at contacts points of cells in a face-centered cubic lattice. To organize the surface into flat connectors and curved actuators, the simplest choice for the shape of the connector is a square, and the geometry is therefore defined by a regular geometric shape composed of 12 squares representing the connectors. These 12 surfaces are connected using hexagons and octagons to form a polyhedron as shown in Fig. 1(b). However, the angles between the surfaces are sharp and make it difficult to move/rotate, so the authors replaced hexagonal and octagonal planes with curved surfaces to obtain continuous surfaces as shown in Fig. 1 (c) and (d).

Catom actuation includes *Latch* (stick to each other) and *Actuate* (move around each other) steps. The Catom surface is insulating and it creates a coupling capacitor when in contact with another Catom. If the electrodes at the inner side of their surface are charged to different potentials, as shown in Fig. 2, an electrostatic force will be produced to either latch or actuate the Catoms. The Catom surfaces (at the contact point) are designed to be flat, so the electrostatic force  $F_e$  is given by

$$F_e = \frac{\varepsilon_0 A V^2}{2d^2} \tag{1}$$

where  $\varepsilon$  is the vacuum permittivity, V is their electrode voltage difference, and A and d are the overlap area and distance of the two Catom surfaces, respectively.

To increase the latch force when two Catoms are in contact, design options include increasing A and V and/or decreasing d. However, the Catom surface size (determines A) and thick-

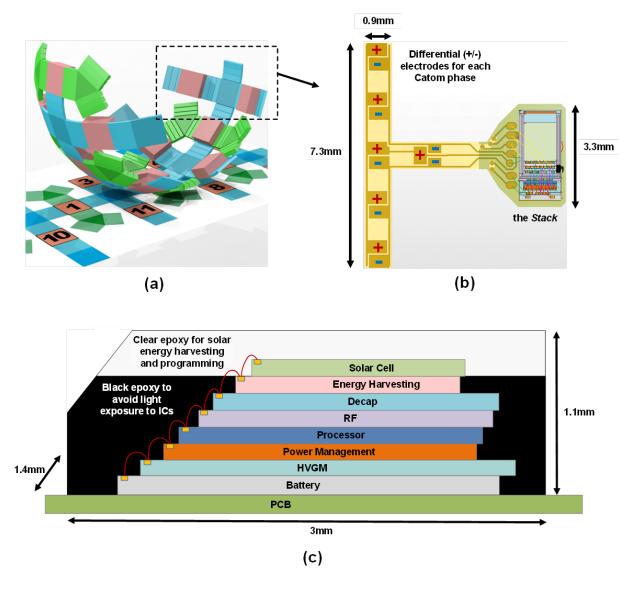

Fig. 3. (a) The disassembled view of a Catom [1]; (b) the Flex-board design with the micro-controller stack and differential high voltage electrodes, and (c) the diagram showing the stack design with multiple custom IC layers.

ness/flatness (determines d) are limited by the resolution and cost of the fabrication process. Due to this, the most effective way to increase force is by applying higher voltages on the electrodes. With a  $10 \times$  voltage on the Catom surface, a  $100 \times$  larger force can be produced, which significantly increases the structural strength of PM in latch positions.

When PM re-configures and the Catoms need to be actuated, the generation of electrostatic force becomes more complex. To move a Catom in the right direction, it needs to change voltage on its multiple surface electrodes according to the condition of their adjacent Catoms. Both attractive force (by using +/- voltage on the 2 Catom surface) and repulsive force (+/+ or -/- voltage) may be used to create the proper force vector on a Catom. Furthermore, during the intermediate states of a Catom movement, the equivalent A and d of its surfaces will continually change, calling for sophisticated control of voltage and timing. In the following sections, we introduce our design for the Stack, a multi-die system that controls the Catom's communication, computation, actuation and power management, emphasizing a specially designed high voltage generation chip that enables a flexible actuation control in a 3-D PM network.

## B. The Stack: Micro-Controller inside the Catom

The micro-controller for the Catom is a core part of PM hardware design, as it determines the scale, lifetime, intelligence and even physical properties of a PM system. In this paper, we propose that the Catom's micro-controller consist of a stack of custom-designed integrated circuits (ICs), with the Stack connected to the Catom's surfaces via a flexible PCB board, as shown in Fig. 3.

The Stack consists of multiple custom IC layers (in bare die form) with different functionalities. A low power processor IC (ARM Cortex M0+), combined with the solar cell IC, provides the programming interface for the Stack via a Global Optical Communication protocol [21]. The protocol adopts

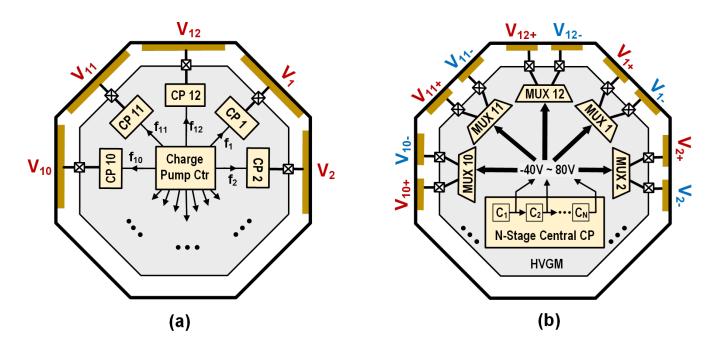

Fig. 4. (a) The conventional Catom driving circuit that has 12 charge pumps to drive 12 positive electrodes and (b) HVGM with single charge pump and 12 high voltage multiplexers to drive 12 pairs of +/- electrodes.

the solar cell as a light receiver, and the external host can synchronize and send commands to one or more Catoms with only 100pJ/bit energy efficiency. When the Catom needs to send a message back to the host, it radios out the data through the short-range RF IC in the Stack. In addition to providing duplex communication, the processor IC also works with the high voltage generation chip (introduced in Section III) to actuate the Catom intelligently using electrostatic force. Connectivity between IC layers in the Stack is achieved by M-Bus [22], an ultra-low power chip-to-chip bus design that uses 4 I/O pads.

The Stack is powered with an integrated thin-film battery layer [20]. Due to the small Catom size, the battery has limited capacity ( $6\mu$ Ah), so we integrate an energy harvesting IC to harvest energy from the solar cell and extend Stack lifetime. In a condition with stable ambient light, the energy harvesting IC, along with the decap layer for energy storage and power management IC for power distribution, can produce sufficient energy for the Stack and enable energy autonomous operation.

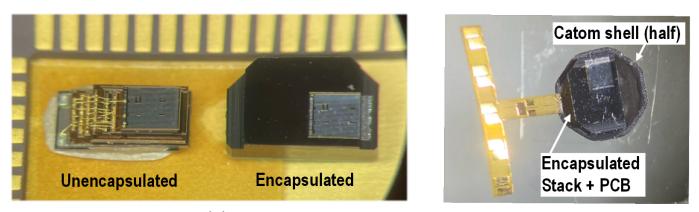

To fit the micro-controller into a Catom, the dies are thinned to  $100\mu$ m each, and stacked together using wire-bonds for their interconnection. The stacked dies are encapsulated in black epoxy to protect against light and contaminants, while only exposing the solar cell at the top for energy harvesting and programming purposes. The encapsulated Stack is then attached to a flexible PCB (only  $80\mu$ m thick), and the highvoltages provided by the Stack are routed through differential (+/-) electrodes to the Catom's surfaces. The differential electrode on each surface makes it easier to implement the high voltage generation chip, and enables better alignment when two Catoms begin making contact. Overall Stack size is  $3\times1.4\times1.1$ mm, and the micro-controller (including PCB) adds 8.8mg to the Catom weight.

# C. HVGM: Energy-Efficient Scheme for Capacitive Actuators

The property of electrostatic actuation determines that we only need to generate high voltages on a purely capacitive load, with little DC current consumption induced on that load. In PM and many other capacitive MEMS actuators, the load capacitance can be small, in the pF range. This creates a very different condition from that of a common high-voltage converter, where increasing the power efficiency under a certain load current is more important than reducing the power overhead to get high voltages. Compared to inductor-based voltage converters [13], switched-capacitor implementations such as Dickson charge pumps are more suitable for low power scenarios [6][7]. However, there are few works that achieve both a large voltage conversion ratio (20×) and the requisite ultra-low power consumption (sub- $\mu$ W).

Moreover, the 12-phase Catom model requires that each of the phase electrodes be individually controlled. With the conventional driving scheme shown in Fig. 4a, each electrode needs to be driven by a separate charge pump, and the charge pump clocks  $f_1 - f_2$  are toggled by a local controller to change their output voltages  $V_1 - V_2$ . Though it is straight forward, this scheme leads to excessive power and area overhead due to the duplication of charge pumps and the clock distribution network. In the envisioned industrial PM systems composed of thousands or even millions of Catoms, power overhead is critical due to the difficulties of power delivery and heat dissipation, while chip area is directly associated with the manufacturing cost per Catom.

Instead of having multiple charge pump copies for the 12 electrodes (capacitive load), the HVGM (Fig. 4b) only possesses a single pump (the central charge pump), which generates a variety of voltages from -40V to 70V, sampled from the charge pump output and all the intermediate stages.

Fig. 5. Top-level diagram of the proposed HVGM chip.

The design leverages a novel high-voltage multiplexer (HV-MUX) that selects from the charge pump voltages and drives each electrode with a unique voltage selection, achieving individual control of the Catom phases. Since a HV-MUX consumes much less power and area than a charge pump, the HVGM greatly amortizes the power and cost overhead to support 12 electrodes with the high-voltage conversion ratio. Compared to the conventional scheme that uses only positive voltages, the HVGM divided its electrodes into Vn+ and Vn- pairs, taking advantage of the negative voltage to create a larger voltage across the +/- electrodes and enhance the actuation force. Moreover, unlike charge pumps that need to be frequently turned on and off in a conventional scheme, the HVGM central charge pump is always running at its steady state, and the electrode voltage change is simply achieved by selecting different voltages with the HV-MUX. In this manner, we avoid discharge and recharge of the flying capacitors and other parasitic nodes in the charge pump, further reducing the active power of the HVGM to sub- $\mu$ W levels.

#### **III. CIRCUIT IMPLEMENTATION OF HVGM**

## A. Central Charge Pump

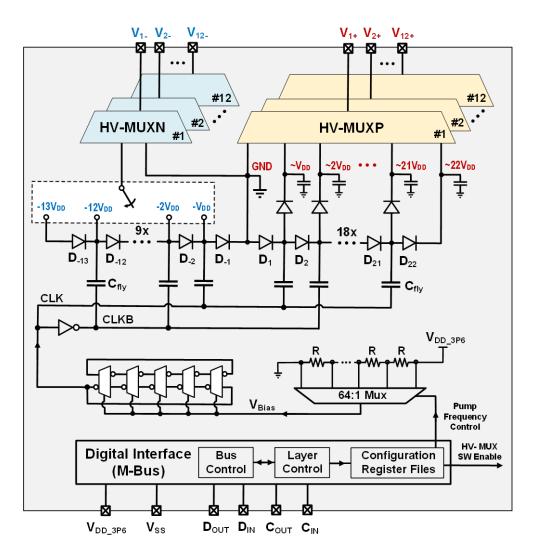

Fig. 5 shows the top-level schematic of the proposed HVGM chip. As explained in the previous section, a single Dickson charge pump is implemented with 22 positive stages  $(D_1 - D_{22})$ , 13 negative stages  $(D_{-13} - D_{-1})$  and a 3.6V supply/clock. Given the charge pump stages and the supply voltage, the charge pump generates up to 70V and down to -40V, which are the maximum achievable voltages allowed in this process. The flying capacitor  $C_{fly}$  is implemented with the MOM capacitor provided by the process, and it can withstand 70V voltage stress across it while maintaining negligible leakages. The central charge pump's output along with its intermediate voltages after each stage are individually selected by 12 positive and negative high-voltage multiplexers (HV-MUXP and HV-MUXN, respectively) to drive the Catom electrodes. During Catom actuation, the voltage changes at the electrodes are also controlled by HV-MUXs, decoupling the central charge pump from the electrodes and ensuring it continually operates in steady state for minimized switching loss.

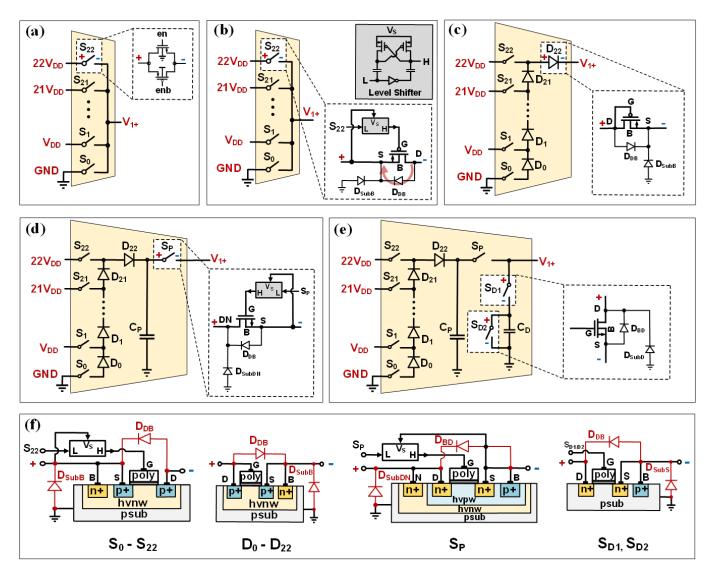

Fig. 6. (a) a conventional analog multiplexer with transmission gate; (b) a level-shifted high-voltage analog multiplexer that has a risk of reverse current (red arrow); (c) the improved high-voltage multiplexer with current-blocking diodes; (d) further improved high-voltage multiplexer with switched-capacitor resistance to limit peak current; (e) the final high-voltage multiplexer implementation with controlled discharge path and (f) device details and cross-section view in (e).

We note that the frequency of the central charge pump determines the maximum average power that can be delivered to the electrodes. For example, if all 12 electrodes need to be activated simultaneously with a large voltage swing (e.g., 0 to 70V), a faster clock frequency is required to maintain the steady state of the central charge pump while it draws more power from the supply. The clock frequency is generated locally and can be tuned with the digital interface and the reconfigurable 64:1 bias voltage selector explained in Section III.D.

To mitigate the power spikes that could occur in the central charge pump, positive intermediate voltages from the charge pump are rectified and buffered with storage capacitors before connecting to HV-MUXP. However for the negative intermediate voltages from the charge pump, they cannot be directly selected by a similar design of HV-MUXN due to the device type limit in this process. Hence, we used a wire-bond selection at chip level (the box indicated with

a dashed line in Fig. 5) to assist in the negative voltage multiplexing from  $-13V_{DD}$  -  $-V_{DD}$ . Then the on-chip HV-MUXN is implemented with a simpler design that only selects from either a negative voltage or ground voltage. Seen as a differential voltage across two Catom electrodes, the HV-MUXN provides a coarse voltage selection of ~40V, while the HV-MUXP provides fine grain control with a step size of ~3V across 70V. The details of designing the HV-MUXP and HV-MUXN will be explained in the following sections.

# B. HV-MUX for Positive Electrodes (HV-MUXP)

The HVGM scheme greatly amortizes the circuit's area and power overhead by employing a single central charge pump with 12 high-voltage multiplexers. However, a main challenge for the HVGM is the implementation of the multiplexer circuit that works with high voltages but maintains low power/leakage. Fig. 6(a) shows a conventional analog

Fig. 7. (a) Implementation of HV-MUXN similar to its positive counterpart but with reverse current issue. (b) the actual HV-MUXN implementation with dual voltage selection and poly-resistor to limit the current.

multiplexer for electrode #1, where the mux switches  $S_1 - S_{22}$ are implemented with transmission gates. If the voltage to be multiplexed exceeds  $V_{DD}$ , a level shifter is required to boost the control signal to a higher DC level while keeping a regular voltage swing on  $V_{GS}$  to avoid gate oxide breakdown. Fig. 6(b) shows a PMOS-only implementation with a clocked level shifter [19] for lower static power. The PMOS body is connected to its source to avoid well leakage, but this also creates a parasitic diode from drain to body  $(D_{DB})$  that results in a large reverse current when the electrode voltage is larger than the charge pump's intermediate voltages. For example, if  $S_{22}$  is turned on to drive the electrode with the highest voltage  $(22V_{DD})$ , the charge on that electrode will then leak away through  $S_0 - S_{22}$ , causing a failure to maintain the high voltage for actuation. To block the reverse current from the electrode to the charge pump, we therefore add diodes  $D_0 - D_{22}$ , which sit in the opposite direction from the parasitic diode of  $S_0 - S_{22}$ , as shown in Fig. 6(c).  $D_0 - D_{22}$  are arranged with serial connections, lowering the reverse voltage stress on each diode to be within  $V_{DD}$  and further reducing their reverse current (leakage) to sub-pA levels. Though the electrode will have a larger conduction loss due to the serial-connected diodes, the overhead is quite negligible in our measurements because of the high-voltage and low-current condition.

A second challenge manifests when a voltage switch  $S_i$  (i ranges from 1 to 22) ramps up the electrode voltage  $V_{1+}$ , drawing a large in-rush charge from the central charge pump. Even though there are buffer capacitors at each stage of the central charge pump, we may still see large voltage drops on any of the intermediate voltages ( $V_{DD}$  to  $22V_{DD}$ ). Although the intermediate voltages can be gradually restored by the central charge pump, their sudden change can cause a failure of the level shifter, which is not recoverable once triggered. This is because the level shifter operates with a clock that constantly "refreshes" its output based on a stable DC value ( $V_S$ ), and it can lose track when the DC value changes abruptly within a clock cycle. Hence, the charge transfer rate from the pump to electrodes must be carefully limited to guarantee stable voltages at all electrodes. In the HVGM, we implement a switch  $S_P$  after the last diode  $D_{22}$  along with a buffer capacitor  $C_P$  as shown in Fig. 6(d) to form a currentlimiting resistance between the central charge pump and the electrode. The equivalent resistance in this path can be tuned by changing the switching frequencies of  $S_P$  and  $S_i$ , trading off the electrode charging speed with the power drawn from the central charge pump. The capacitance of  $C_P$  (200fF) is small compared to that of the electrode (10s of pF), so the voltage swing on  $C_P$  is large and cannot be used as  $V_S$  by the level shifter. Instead we level shift the  $S_P$  control signal based on the electrode voltage  $V_{1+}$ , which is slowly charged and hence easy to track, and we implement  $S_P$  with an NMOS transistor accordingly.

A third challenge is that with the addition of diodes  $D_0 - D_{22}$ , the central charge pump can only provide charge to the electrode (i.e., it cannot discharge). With no DC load current on the electrode, its voltage will decrease extremely slowly (through leakage), which is problematic for periodic actuation. Hence, we implement an intentional discharge path with switched-cap resistor  $S_{D1}$ ,  $S_{D2}$ , and  $C_D$ . By using the regular supply voltage to control switches  $S_{D1}$  and  $S_{D2}$  in a non-overlapping way, we limit the charge transfer to  $C_D V_{DD} V_{th}$  per cycle, and the electrode is gradually discharged at a controllable speed. When not discharging, both  $S_{D1}$  and  $S_{D2}$  are turned off, creating a stack effect to strongly reduce leakage at the electrode.

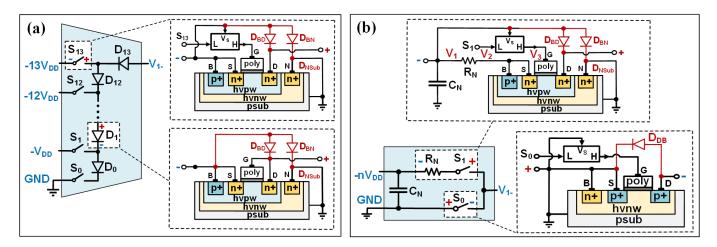

## C. HV-MUX for Negative Electrodes (HV-MUXN)

Previous sections explained the advantages of having the electrodes driven by negative voltages, thereby increasing the voltage stress and achieving more electrostatic force. However, multiplexing the negative voltage requires a different approach than that proposed for positive voltages in the preceding section. In the HV-MUXN, the counterpart of the HV-MUXP, all switches are implemented with NMOS transistors because their control signals are level shifted from a lower potential side (from the central charge pump), as shown in Fig. 7(a). A high-voltage-n-well (hvnw) layer separates the NMOS body (P-type diffusion biased with negative voltage) from the chip

Fig. 8. Leakage-based ring oscillator [18] with bias voltage  $V_{BN}$  controlling the output frequency.

Fig. 9. HVGM die photo.

substrate (grounded) to avoid substrate leakage. However, diodes  $D_0 - D_{13}$  have the same parasitic diodes ( $S_{BD}$  and

$S_{BN}$ ) as the switches  $S_0 - S_{13}$ , failing to block the reverse current if it occurs at the switches. Further, switches  $S_{D1}$ ,  $S_{D2}$  and  $S_P$  would need to be PMOS, which is not possible since their n-well, which is connected to the negative voltage, would short to the P-type substrate through the well diode.

We instead opt for a simpler binary HV-MUXN that selects between one of the negative voltages and GND (Fig. 7(b)). While  $S_1$  uses an NMOS with an hvnw layer,  $S_0$  is implemented with PMOS transistors and its gate control signal is level shifted to toggle between  $-V_{DD}$  and ground. Since it is not possible to implement the switched-capacitor resistor with  $S_P$ , we use a poly resistor  $R_N$  to limit the current from the central charge pump to the negative electrode. However, the resistance of  $R_N$  is constrained to sub-M $\Omega$  due to chip area limits, which is insufficient to limit the current flow to  $\mu A$ levels under a large negative voltage (-40V). We therefore make  $S_1$  a weakly turned-on switch that endures most of the voltage stress and effectively limit the current through it. This is achieved by level shifting its gate voltage  $V_3$  from  $V_1$ (instead of  $V_2$  in the normal case) as shown in Fig. 7(b). Since the level shifter provides a shift that is smaller than  $V_{DD}$ , we have

$$V_G = V_3 < V_1 + V_{DD}$$

(2)

Meanwhile, when the NMOS transistor is turned on,

$$V_2 < V_3 - V_{TH}$$

(3)

Combining (2) and (3) we have

$$V_2 < V_1 + V_{DD} - V_{TH}$$

(4)

or equivalently

$$V_2 - V_1 < V_{DD} - V_{TH} (5)$$

This indicates that the voltage across  $R_N$  is always limited to less than  $(V_{DD} - V_{TH})$  no matter how large the voltage is between the pump and the electrode. The current flow is therefore also limited to  $(V_{DD} - V_{TH})/R_N$  independent of the voltage being multiplexed.

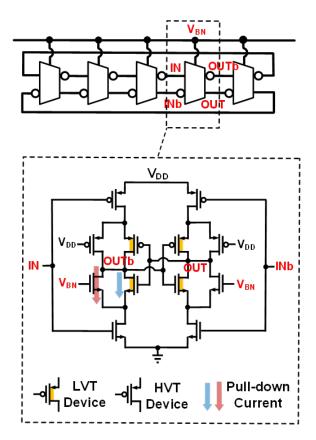

# D. Peripheral Circuits in HVGM

The central charge pump and HV-MUXs provide a flexible and efficient way to achieve high-voltage actuation. The control logic for them can be summarized into two classes: 1) switch enable signals and 2) the frequency control signal, as shown in Fig. 5. The enable signals control the switching activities of the HV-MUXP and HV-MUXN, multiplexing and driving the electrode with proper voltages defined by the user. The frequency control signal is achieved by a leakage-based ring oscillator [18] as shown in Fig. 8. The ring oscillator consists of leakage-based inverters with an additional low-Vth (LVT) device pair in the middle. When the input voltage flips, the leakage path through the LVT latch controls the delay of output toggling and determines the oscillation frequency. Further tuning of the frequency can be achieved by adding a current path with the parallel transistors that are biased

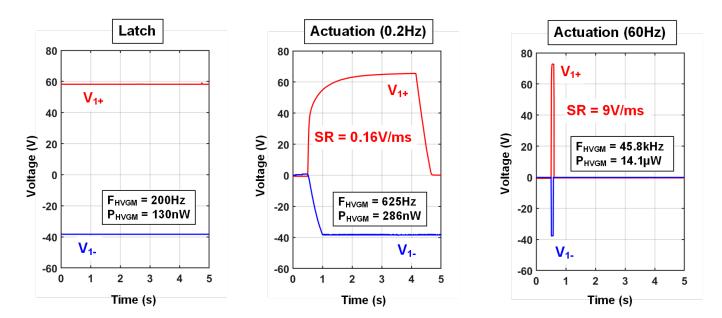

Fig. 10. Measured transient waveform showing the electrode voltage to latch (left), slow actuate (middle) and fast actuate (right).

with  $V_{BN}$  (the PMOS parallel legs are disabled by biasing at  $V_{DD}$ ). The voltage  $V_{BN}$  is generated by a poly-resistor divider and selected with a 64-to-1 multiplexer. It achieves a broad band frequency tuning range (30Hz-1MHz measured at room temperature) for the charge pump and HV-MUXs, and therefore provides a wide range for Catom actuation speed.

The enable and frequency control signals are stored in configuration register files in the M-Bus block. As we previously mentioned, the HVGM is a member layer (one of the chips/bare-dies that build up the Stack) in the Catom stack, and it receives the actuation code through the  $C_{IN}$  and  $D_{IN}$  terminals and passes its working state to the other layers through  $C_{OUT}$  and  $D_{OUT}$ . When the HVGM is not changing its actuation mode (e.g., latching to another Catom/HVGM), most of the M-Bus block is power gated and only draws static current, further reducing the power overhead for the digital circuits.

### **IV. MEASUREMENT RESULTS AND ANALYSIS**

# A. HVGM Measurement Results

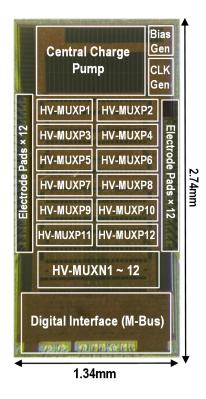

HVGM is fabricated in a 180nm HV BCD process and occupies  $3.67mm^2$  including the area for 24 pads that connect to positive and negative electrodes in a Catom. Fig. 9 shows the HVGM die photograph.

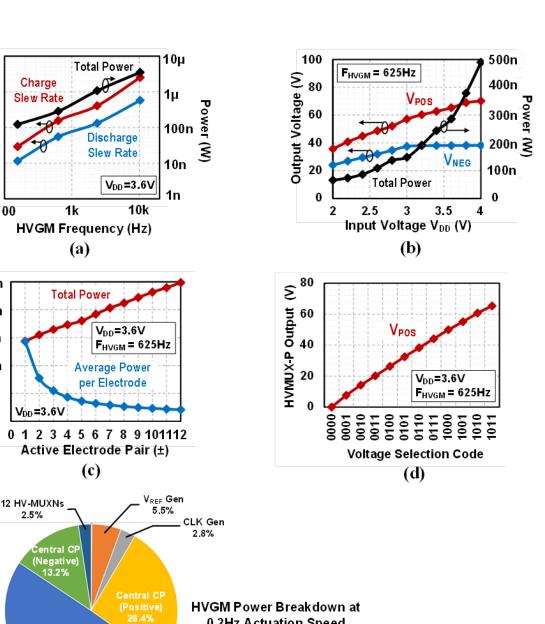

In the idle state, the HVGM consumes 7nW power at room temperature from a 3.6V supply. In the latch state, it consumes 130nW to sustain a DC voltage of 100V on one pair of the +/- electrodes. When in the actuation state, however, the HVGM can trade off its active power with the actuation speed that is determined by the slew rate charging/discharging the electrode. Fig. 10 shows the transient waveform of the HVGM driving a 10pF electrode with the minimum and maximum actuation speeds. In the slowest actuation setting, the HVGM operates at a frequency of 625Hz, consuming 286nW average power to charge an electrode at 155V/s slew rate, which is sufficient for PM to achieve a 0.2Hz periodic actuation with 103V voltage swing (29x voltage gain). With the same load condition, the HVGM can support up to 60Hz actuation by increasing its frequency to 46kHz, consuming 14.1 $\mu$ W. The increase in power with actuation frequency is mainly due to the parasitic capacitance of  $C_{fly}$ , but the power/current loss due to the diode parasitics will be noticeable if the actuation frequency increases further.

Fig. 11(a) further demonstrates the linear relationship between the voltage slew rate and HVGM power, showing a constant energy efficiency with different actuation speed. The HVGM benefits from the single pump topology by significantly amortizing the charge pump power at higher electrode counts. This is confirmed by the measurement results in Fig. 11(b). With more electrodes being actively transitioned, the average power per electrode reduces from 286nW (1 electrode pair) to 41nW (12 electrode pairs). Fig. 11(c) shows the maximum HVGM voltage on the positive and negative electrodes with different supply voltages. In addition to driving the electrodes with the maximum voltage, the HVGM also provides programmable voltages with a 5V step depending on the actuation command type, as shown in Fig. 11(d). Fig. 11(e) shows the power breakdown of HVGM when it activates the electrode with 0.2Hz frequency (shown in the middle graph of Fig. 10).

Table I compares HVGM performance with prior on-chip high voltage generators. Though their load conditions vary, HVGM shows the highest voltage gain and lowest power consumption when generating high voltages that are sufficient for PM and many other micro-robot actuators. It is also the first to have fully programmable high voltages on multiple output ports, which further extends its application range towards IoT.

## B. Stack and Catom Integration

The HVGM die is thinned and stacked with other ICs, as explained in Section II.B, to form the Stack that resides in the

Fig. 11. (a) Measured HVGM power versus the electrode slew rate at different clock frequencies; (b) measured HVGM output voltage and power with different supply voltages; (c) measured HVGM power with different number of electrode being activated; (d) measured HVGM output programmability; (e) HVGM power breakdown with 0.2Hz actuation speed (the percentage of circuit blocks comes from post-pex simulation).

0.2Hz Actuation Speed  $(P_{TOTAL} = 285.8nW)$

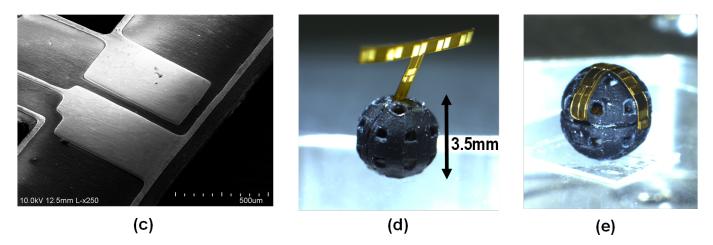

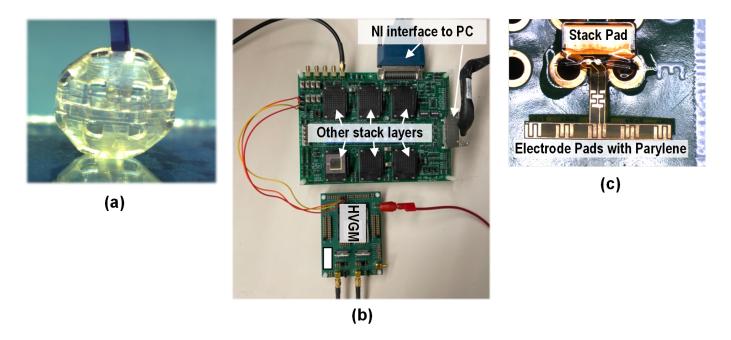

Catom. Fig. 12(a) shows the Stack photo without and with the black epoxy, with 3×1.4×1.1mm size and 4.8mg weight after the encapsulation. The encapsulated Stack is then connected to the flexible PCB ( $80\mu m$  thick and 4mg weight) and fit into a Catom shell with  $\sim$ 3.5mm diameter, as shown in Fig. 12(b). The high voltage pads from the Stack (HVGM die) are wirebonded to the flexible PCB, and connected to the differential electrodes that will be attached to the Catom surfaces. Fig. 12(c) shows the microscope image for a pair of the differential

12 HV-MUXPs 49.6%

(e)

10<sup>4</sup>

**10**<sup>3</sup>

10<sup>2</sup>

10

10<sup>0</sup>

500n

400n

100n

0

0

100

Slew rate (V/sec)

electrodes. The metals are carefully deposited and cleaned for a flat surface, which guarantees close contact (smaller gap distance) with another Catom's electrodes and increases the electrostatic force.

The Stack integration, the flexible PCB and full Catom shell are shown in Figs. 12(d) and (e). For the demonstration we only include the electrodes for the upper hemisphere of the Catom. In real applications, the Catom shell will be fabricated with a transparent material (Fig. 13(a)) that enables

TABLE I PERFORMANCE SUMMARY OF HVGM AND COMPARISON WITH PRIOR WORKS

| Publication*             | Process      | Circuit Type                 | $V_{IN}$     | V <sub>OUT</sub> | Voltage<br>Gain | Output<br>Frequency | Power ***                              | Load<br>Condition | Output<br>Adjustable | Number<br>of Output |

|--------------------------|--------------|------------------------------|--------------|------------------|-----------------|---------------------|----------------------------------------|-------------------|----------------------|---------------------|

| JSSC<br>2019 [6]         | $0.35 \mu m$ | Charge Pump                  | 3.3V         | 32.6V            | 9.9             | DC                  | $97\mu W@DC$                           | -                 | No                   | 1                   |

| ISSCC<br>2014 [7]        | 65nm         | Charge Pump                  | 2.75V        | 34V              | 12.3            | DC                  | -                                      | -                 | No                   | 1                   |

| ISCAS<br>2011 [8]        | $1 \mu m$    | Charge Pump +<br>Rectifier   | 5V           | 33V              | 6.6             | DC -<br>500Hz**     | -                                      | 10pF              | No                   | 1                   |

| TCAS1<br>2015 [9]        | $0.8 \mu m$  | HV Amp +<br>Multiplexer      | 5V &<br>300V | 290V             | 58.0 &<br>0.97  | DC                  | 90mW @ DC                              | 10nF              | No                   | 1                   |

| ISCAS<br>2016 [10]       | $0.8 \mu m$  | Voltage Doubler              | 15v          | 360.5V           | 24.0            | DC - 60Hz           | -                                      | -                 | No                   | 1                   |

| ICECS<br>2014 [11]       | $0.13 \mu m$ | Charge Pump                  | 1.2v         | 10.6V            | 8.8             | DC -<br>100kHz**    | $759 \mu W @100 kHz$                   | z 1pF             | Yes                  | 1                   |

| Ind. Elect.<br>2013 [12] | $0.6 \mu m$  | Charge Pump                  | 6v           | 51V              | 8.5             | DC -<br>1kHz**      | -                                      | 1pF               | No                   | 1                   |

| This work                | $0.18 \mu m$ | Charge Pump +<br>Multiplexer | 3.6v         | 103V             | 28.6            | DC - 60Hz           | 130nW@DC<br>286nW@0.2Hz<br>14.1µW@60Hz | 10pF              | Yes                  | 12                  |

\* All works in the table are fully integrated high-voltage generators with no/light load.

\*\*\*\* Some works did not report power number (but only efficiency) because they are not power constrained.

(b)

Fig. 12. (a) The Stack photo with and without the black epoxy encapsulation; (b) encapsulated Stack fit in a half Catom shell and connected to the flexible PCB; (c) microscope image showing the differential electrode design on the flexible PCB; (d) full Catom with the Stack in it and an unattached flexible PCB; (e) full Catom with the Stack and flexible PCB attached to its surfaces.

Fig. 13. (a) Catom hardware with transparent shell for solar energy harvesting and communication; (b) test setup consisting of discrete Stack layers in PGA packages for functional check; (c) test setup consisting of the parylene-coated (insulator) flex board to generate the attraction force for mass attachment.

the light to go through the shell and be received by the Stack. To quantize the impact of Catom shell on the PV energy harvesting, we measured the PV power with a Catom shell and compares it to that without the Catom shell. Under a strong 100k lux LED light, the Catom shell only attenuated the light intensity by 11.6%. Under normal light conditions (300 - 3k lux), the Catom shell even increased the PV power because the light is scattered or flared by the transparent Catom shell. When the Stack is powered up, we have measured an electrostatic force sufficient to adhere/release a >1mg mass with the high voltages generated by the HVGM. Fig. 13(b) shows the measurement setup to check the Stack functionality with discrete Stack layers in PGA packages. Fig. 13(c) shows attraction force test setup with the T-shaped flex-board, coated with Parylene and generate the attraction force for the mass. We are currently running a real latching and actuation test with two fabricated Catoms, and will be publishing the new results soon.

## V. CONCLUSION

This paper presents a high-voltage-generation-andmultiplexing (HVGM) chip in a 180nm HV BCD process, which is specifically designed for the actuation of Catoms in PM and other capacitive micro-actuators. The HVGM chip can individually control 12 pairs of +/- electrodes in a Catom, with its novel design on the high voltage multiplexers to either maintain a high voltage at the electrode (for latch) or change its voltage at a controlled speed (for actuation). The HVGM consumes only 130nW in latch mode and 286nW - 14.1 $\mu$ W in actuation mode depending on the speed, achieving 0 – 103V programmable voltages on the 12 electrode pairs. To achieve fully autonomous operation, the HVGM is integrated with other chip layers to form a complete microsystem of stacked dies, including a processor, radio, energy harvester and battery. The fabricated Stack is  $4.6mm^3$  size and weights 4.8mg, and it is integrated with a 3.5mm Catom and shows sufficient adhesive force and release of a >1mg mass using the high voltages generated by the HVGM.

### REFERENCES

- B. Piranda and B. Julien, "Designing a quasi-spherical module for a huge modular robot to create programmable matter", Autonomous Robots Journal, vol. 42, no. 8, 2018

- [2] P. Hołobut, M. Kursa and J. Lengiewicz, "A class of microstructures for scalable collective actuation of Programmable Matter," 2014 IEEE/RSJ International Conference on Intelligent Robots and Systems, pp. 3919-3925, 2014.

- [3] B. Piranda and B. Julien, "Geometrical Study of a Quasi-Spherical Module for Building Programmable Matter", 13th International Symposium on Distributed Autonomous Robotic Systems (DARS)", London, UK, 2016

- [4] K. Thadeu, B. Piranda and B. Julien, "Efficient Scene Encoding for Programmable Matter Self-Reconfiguration Algorithms", 28-th ACM Symposium On Applied Computing. Association for Computing Machinery (ACM), pp. 256 - 261, 2017.

- [5] P. Florian, N. Nills, B. Piranda and B. Julien, "GAPCoD : A Generic Assembly Planner by Constrained Disassembly", 19th International Conference on Autonomous Agents and Multiagent Systems (AAMAS 2020), May 9-13, 2020.

- [6] M. Marx, S. Rombach, S. Nessler, D. De Dorigo and Y. Manoli, "A 141- $\mu$  W High-Voltage MEMS Gyroscope Drive Interface Circuit Based on Flying Capacitors," in IEEE Journal of Solid-State Circuits, vol. 54, no. 2, pp. 511-523, Feb. 2019.

- [7] Y. Ismail, H. Lee, S. Pamarti and C. -K. K. Yang, "A 34V charge pump in 65nm bulk CMOS technology," 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 408-409, 2014.

- [8] M. E. Karagozler, A. Thaker, S. C. Goldstein and D. S. Ricketts, "Electrostatic actuation and control of micro robots using a post-processed high-voltage SOI CMOS chip," 2011 IEEE International Symposium of Circuits and Systems (ISCAS), pp. 2509-2512, 2011.

- [9] S. Dai, R. W. Knepper and M. N. Horenstein, "A 300-V LDMOS Analog-Multiplexed Driver for MEMS Devices," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 12, pp. 2806-2816, Dec. 2015.

- [10] P. Beaulieu, A. H. Alameh, M. Menard and F. Nabki, "A 360 V high voltage reconfigurable charge pump in 0.8μm CMOS for optical MEMS applications," 2016 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1630-1633, 2016.

- [11] A. H. Alameh, A. Robichaud and F. Nabki, "A reconfigurable charge pump in 0.13 m CMOS for agile MEMS actuation," 2014 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 670-673, 2014.

- [12] A. Emira, M. AbdelGhany, M. Elsayed, A. M. Elshurafa, S. Sedky and K. N. Salama, "All-pMOS 50-V Charge Pumps Using Low-Voltage Capacitors," in IEEE Transactions on Industrial Electronics, vol. 60, no. 10, pp. 4683-4693, Oct. 2013.

- [13] M. Lok, E. F. Helbling, X. Zhang, R. Wood, D. Brooks and G. -Y. Wei, "A Low Mass Power Electronics Unit to Drive Piezoelectric Actuators for Flying Microrobots," in IEEE Transactions on Power Electronics, vol. 33, no. 4, pp. 3180-3191, April 2018.

- [14] J. S. Rentmeister, M. H. Kiani, K. Pister and J. T. Stauth, "A 120–330V, Sub-A, 4-Channel Driver for Microrobotic Actuators with Wireless-Optical Power Delivery and over 99% Current Efficiency," 2020 IEEE Symposium on VLSI Circuits, pp. 1-2, 2020.

- [15] S. Chaput, D. Brooks and G. Y. Wei, "21.5 A 3-to-5V input 100Vpp output 57.7mW 0.42% THD+N highly integrated piezoelectric actuator driver," 2017 IEEE International Solid-State Circuits Conference (ISSCC), pp. 360-361, 2017.

- [16] Y. Li, B. L. Dobbins and J. T. Stauth, "An 80-117V Pseudo-Adiabatic Drive Circuit for Microrobotic Actuators with Optical Power Delivery and Peak Power Reduction Factor over 14×," 2020 IEEE Custom Integrated Circuits Conference (CICC), pp. 1-4, 2020.

- [17] Y. Peng et al., "A 286nW, 103V High Voltage Generator and Multiplexer for Electrostatic Actuation in Programmable Matter," 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), pp. 158-159, 2022.

- [18] I. Lee, D. Sylvester and D. Blaauw, "A Constant Energy-Per-Cycle Ring Oscillator Over a Wide Frequency Range for Wireless Sensor Nodes," in IEEE Journal of Solid-State Circuits, vol. 51, no. 3, pp. 697-711, March 2016.

- [19] Z. Liu and H. Lee, "A 100V gate driver with sub-nanosecond-delay capacitive-coupled level shifting and dynamic timing control for ZVSbased synchronous power converters," Proceedings of the IEEE 2013 Custom Integrated Circuits Conference, pp. 1-4, 2013.

- [20] M. Fojtik et al., "A Millimeter-Scale Energy-Autonomous Sensor System With Stacked Battery and Solar Cells," in IEEE Journal of Solid-State Circuits, vol. 48, no. 3, pp. 801-813, March 2013.

- [21] W. Lim, T. Jang, I. Lee, H.-S. Kim, D. Sylvester, and D. Blaauw, "A 380 pW dual mode optical wake-up receiver with ambient noise cancellation," in Proc. IEEE Symp. VLSI Circuits (VLSI-Circuits), pp. 1–2, June. 2016.

- [22] Y. -s. Kuo et al., "MBus: A 17.5 pJ/bit/chip portable interconnect bus for millimeter-scale sensor systems with 8 nW standby power," Proceedings of the IEEE 2014 Custom Integrated Circuits Conference (CICC), pp. 1-4, 2014.

others pending.

**Gordy Carichner** (M'95) received the B.S.E. and M.S.E. degrees in electrical engineering from the University of Michigan, Ann Arbor, in 1989 and 1991, respectively. He joined Motorola, Inc., Austin, TX, in 1991, designing circuits for 16-b digital signal processors. He returned to the University of Michigan in 1998 to teach VLSI design and to support EDA software. In 2004, he joined Mobius Microsystems, Inc., Ann Arbor, where he designs digital and analog circuits for monolithic RF *LC* clock generators. He holds three U.S. patents with

Yejoong Kim received the Bachelor degree in electrical engineering from Yonsei University, South Korea, in 2008, and the Master degree and Ph.D. degree from the University of Michigan, Ann Arbor, in 2012 and 2015, respectively, all in electrical engineering. He is currently a Research Fellow at the University of Michigan and a Vice President of Research and Development at CubeWorks, Inc. His research interests include subthreshold circuit designs, ultra low-power SRAM, and the design of millimeter-scale computing systems and sensor

Li-Yu Chen received the B.S. degree in electrical engineering from National Taiwan University in 2019 and began work on her graduate degree in electrical engineering at the University of Michigan, Ann Arbor in 2019. Since 2021, she has been a Research Assistant with the Wireless Integrated Circuits and Systems Group (WICS) at the University of Michigan and does research on the fully-autonomous system-on-chip (FASoC) project.

**Yimai Peng** (S'16) received his B.Eng. degree in electrical and computer engineering from Huazhong University of Science and Technology, Wuhan, China, in 2015. He received his M.S. degree and Ph.D. degree in electrical engineering from the University of Michigan, Ann Arbor, in 2017 and 2022, respectively. He is a recipient of the Dwight F. Benton Fellowship at the University of Michigan. In 2022, He joined Qualcomm as a senior engineer to work on circuit research and development for higher energy efficiency and robustness, for various

of processors, servers, and IoT devices. His research interests include low power circuit system designs in power management, energy harvesting, analog front end, and intelligent micro-robot system.

**Rémy Tribhout** is a research engineer in the Optimization, Mobility, NetworkIng (OMNI) team at the Department of Computer Science for Complex Systems (DISC) of FEMTO-ST Institute, University of Franche-Comté (UFC) in France. His work focuses on the Programmable Matter project which follows the Claytronic Atom project from the Carnegie Mellon University. He received his M.S. degree in computer science and telecommunications from the National Institute of Applied Sciences (INSA), Toulouse, France, in 2016. He worked 4 years at

Thales SIX GTS with 3 years spent as a Systems Engineer expatriate in Panama for the project Metro de Panama Linea 2. Since 2022, he leads the startup project Phigi, which develops an interactive clay made of thousands of microbots that self-assemble into any shape, facilitating the collaborative design of industrial products, in collaboration with the University of Michigan and the FEMTO-ST Institute.

**Benoît Piranda** is Associate Professor of Computer Science at the University of Franche-Comté in France. He is part of the computer science department at FEMTO-ST Institute, CNRS. His main domains of research are Distributed Programming, Physical and Visual Simulations of Robots and Computer Graphics (Image Synthesis). He is author of more than 75 international papers in these subjects.

He leads the development of the VisibleSim software which is a behavioral simulator of modu-

lar robots (https://www.programmable-matter.com/simulation). This simulator schedules in parallel codes running in thousands of modules, simulates communications, movements, physical interactions, and various sensors and actuators.

**David Blaauw** (Fellow, IEEE) received his B.S. in physics and computer science from Duke University in 1986 and his Ph.D. in computer science from the University of Illinois at Urbana-Champaign in 1991. Until August 2001, he worked for Motorola, Inc. in Austin, TX, where he was the manager of the High Performance Design Technology group and won the Motorola Innovation award. Since August 2001, he has been on the faculty of the University of Michigan, where he is the Kensall D. Wise Collegiate Professor of EECS. He has published over

600 papers, has received numerous best paper awards and holds 65 patents. He has researched ultra-low-power wireless sensors using subthreshold operation and low-power analog circuit techniques for millimeter systems. This research was awarded the MIT Technology Review's "one of the year's most significant innovations." His research group introduced so-called near-threshold computing, which has become a common concept in semiconductor design. Most recently, he has pursued research in cognitive computing using analog, inmemory neural-networks for edge-devices and genomics for precision health. He was general chair of the IEEE International Symposium on Low Power and a member of the IEEE International Solid-State Circuits Conference (ISSCC) analog program subcommittee. He is an IEEE Fellow and received the 2016 SIA-SRC faculty award for lifetime research contributions to the U.S. semiconductor industry.

Julien Bourgeois is a Professor of computer science with the University of Franche-Comté (UFC), Montbéliard, France. He is also part of the Franche Comté Electronique Mécanique Thermique et Optique-Sciences et Technologies (Femto-ST) Institute (UMR CNRS 6174), UFC, where he is leading the Complex Networks Team. He was an Invited Professor with Carnegie Mellon University, Pittsburgh, PA, USA, from September 2012 to August 2013; with Emory University, Atlanta, GA, USA, in 2011; and with The Hong Kong Polytechnic

University, Hung Hom, Hong Kong, in 2010 and 2011. He is currently leading the topic of system architecture, communication, and networking with Laboratoire d'Excellence (LABEX) ACTION, which is a 10-M funded program that aims to build integrated smart systems (http://www.labex-action.fr/). He collaborated with several other institutions (e.g., the Lawrence Livermore National Laboratory, the Oak Ridge National Laboratory, etc.). He has worked for more than ten years in his topics of interest, and he is the coauthor of more than 70 international publications and communications. Apart from his research activities, he is acting as a Consultant for the French government and for private companies. His research interests include distributed intelligent microelectromechanical systems (MEMS), peer-to-peer (P2P) networks, and security management for complex networks.

Mr. Bourgeois is a member of more than ten program committees of international conferences on his topics of interest and has organized many events. He was the Program Chair of the workshop on Distributed MEMS (dMEMS) in 2010 and 2012, and the 7th International Workshop on Hot Topics in Peer-to-Peer Systems collocated with the IEEE/Association for Computing Machinery 2010 International Parallel and Distributed Processing Symposium; the Program Cochair of the Euromicro International Conference on Parallel, Distributed and Network-Based Processing (PDP) in 2008 and 2010; the Program Vice-Chair of the IEEE International Conference on High Performance Computing and Communications (HPCC) in 2011; the Publicity Chair of the IEEE/International Federation for Information Processing International Conference on Embedded and Ubiquitous Computing (EUC) in 2010 and the IEEE International Symposium on Electromagnetic Compatibility (EMC) in 2012; the General Chair of the IEEE International Conference on Green Computing and Communications (GreenCom) in 2012, the IEEE International Conference on Internet of Things (iThings) in 2012, and the IEEE International Conference on Cyber, Physical and Social Computing (CPSCom) in 2012; the Program Chair of the International Conference on Grid and Pervasive Computing (GPC) in 2012; and the General Chair of the IEEE HPCC in 2014, the IEEE International Conference on Embedded Software and Systems in 2014, and the IEEE Control Systems Society in 2014. In 2005, he created and then chaired all the editions of the Workshop on Modeling, Simulation and Optimization of Peer-to-Peer Environments (MSOP2P) collocated with PDP until 2013.

**Dennis Sylvester** (Fellow, IEEE) received the Ph.D. degree in electrical engineering from the University of California at Berkeley, Berkeley, CA, USA, in 1999.

He held research staff positions at Synopsys, Mountain View, CA, USA, and Hewlett-Packard Laboratories, Palo Alto, CA, USA, as well as visiting professorships at the National University of Singapore, Singapore, and Nanyang Technological University, Singapore. He is currently the Edward S. Davidson Collegiate Professor of Electrical and

Computer Engineering at the University of Michigan, Ann Arbor, MI, USA. His research has been commercialized via three major venture capital-funded start-up companies: Ambiq Micro, Austin, TX, USA, Cubeworks, Ann Arbor, and Mythic, Redwood City, CA, USA. His main research interests are in the design of miniaturized ultralow-power microsystems, touching on analog, mixed-signal, and digital circuits. He has published over 500 articles and holds more than 50 U.S. patents in these areas.

Dr. Sylvester is a member of the Administrative Committee of the IEEE Solid-State Circuits Society and an Associate Editor of IEEE Journal of Solid-State Circuits. He was a Distinguished Lecturer of the IEEE Solid-State Circuits Society. He has received 14 best paper awards and nominations and was named a Top Contributing Author at the International Solid-State Circuits Conference (ISSCC) and the most prolific author at the IEEE Symposium on Very Large Scale Integration (VLSI) Circuits.