# Actes des journées Approches Formelles dans l'Assistance au Developpement du Logiciel (AFADL 2025)

Fabien Dagnat, Olga Kouchnarenko

#### ▶ To cite this version:

Fabien Dagnat, Olga Kouchnarenko. Actes des journées Approches Formelles dans l'Assistance au Developpement du Logiciel (AFADL 2025). Approches Formelles dans l'Assistance au Developpement du Logiciel, Jun 2025, Pau, France. 2025. hal-05106227

#### HAL Id: hal-05106227 https://hal.science/hal-05106227v1

Submitted on 10 Jun 2025

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Actes des Journées / Proceedings

## Approches formelles dans l'assistance au développement du logiciel (AFADL)

https://gdrgp12025.sciencesconf.org/resource/page/id/1

tenues conjointement avec les Journées du Groupement de Recherche national - Génie de la Programmation et du Logiciel GDR-GPL 2025 à Pau (https://gdrgpl2025.sciencesconf.org)

16-18 juin 2025 / June 16-18, 2025 Pau, France

Avec la collaboration des groupes de travail / With the collaboration of the working groups :

Langages et vérification de programmes (GT LVP) Méthodes de test pour la validation et la vérification (GT MTV2)

#### Éditeurs / Editorial boards

Fabien DAGNAT, Olga KOUCHNARENKO (Co-présidents/Co-chairs AFADL'2025, Pau)

#### Comité de programme / Programme Committee

Idir Ait Sadoune LMF, CentraleSupélec, Université de Paris-Saclay, France

Moussa Amarani Université de Namur, Belgique

Olivier Barais IRISA, Université de Rennes, France

Clara Bertolissi LIS, Université d'Aix-Marseille, France

Marius Bozga VERIMAG, CNRS, France

Jérémy Buisson École de l'air et de l'espace, France

David Chemouil DTIS, ONERA et Université de Toulouse, France

Horatiu Cirstea LORIA, Université de Lorraine, France Frédéric Dabrowski LIFO, Université d'Orléans, France Lab-STICC, IMT Atlantique, France LS2N, Nantes Université, France Lydie Du Bousquet LIG, Université Grenoble Alpes, France

Sophie Ebersold IRIT, Université de Toulouse, France Mohammed Foughali IRIF, Université de Paris, France Université de Sherbrooke, Canada Laure Gonnord LCIS, Grenoble INP - UGA, France

Pierre-Cyrille Héam FEMTO-ST, Université Marie et Louis Pasteur, France

Ludovic Henrio CNRS, LIP, France

Aurélie Hurault IRIT, Toulouse INP, France

Nikolai Kosmatov Thales Research and Technology, cortAIx Labs , France Olga Kouchnarenko FEMTO-ST, Université Marie et Louis Pasteur, France

Natalia Kushik SAMOVAR, Télécom SudParis, Institut Polytechnique de Paris, France

Régine Laleau LACL, Université Paris-Est Créteil, France

Thierry Lecomte CLEARSY, France

Delphine Longuet Thales Research and Technology, cortAIx Labs, France

Frédéric Mallet I3S, Université Côte d'Azur, France Célia Picard ENAC, Université de Toulouse, France Clément Quinton CRIStAL, Université de Lille, France

Antoine Rollet LaBRI, Bordeaux INP, France

Julien Signoles Université Paris-Saclay, CEA, List, France

Nicolas Stouls CITI, INSA Lyon, France Ciprian Teodorov Lab-STICC, ENSTA, France

Benoît Valiron LMF, CentraleSupélec, Université de Paris-Saclay, France

Laurent Voisin Systerel, France

### Table des matières

| Préface                                                                                                                                                                                                    | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Session AFADL I                                                                                                                                                                                            | 3  |

| Langage de spécification de contexte pour vérifier formellement des propriétés de consentement sur des modèles et du code [Résumé long], Myriam Clouet, Thibaud Antignac, Mathilde Arnaud, Julien Signoles |    |

| Project & Conquer : Élimination de quantificateurs pour la vérification de problèmes d'accessibilité dans les réseaux de Petri, <i>Nicolas Amat, Silvano Dal Zilio, Didier Le Botlan</i>                   | 10 |

| Transformations automatisés de preuves Coq, Alexandre Jean, Nicolas Magaud                                                                                                                                 | 16 |

| Approche neuro-symbolique pour générer un référentiel de test, Eléa Jacquin                                                                                                                                | 21 |

| Session poster AFADL                                                                                                                                                                                       | 25 |

| On the use of generalisation and unification for composing interactions via gate connection, Joel Nguetoum Kenne, Boutheina Bannour, Pascale Le Gall                                                       | 27 |

| Deductive Verification of Synchronous Reactive Programs, Frédéric Dabrowski, Térence Clastres                                                                                                              | 30 |

| Détection et Réparation d'Anomalies en Arithmétique à Virgule Flottante par Analyse Statique, <i>Julien Bortolussi, Dorra Ben Khalifa, Pierre-Loïc Garoche</i>                                             | 33 |

| Session AFADL & LVP                                                                                                                                                                                        | 37 |

| Prouvez vos coloriages : vérification formelle du coloriage de cache de l'hyperviseur Bao, Axel Fer-<br>réol, Laurent Corbin, Nikolai Kosmatov                                                             | 39 |

| BICOQ : une formalisation des bigraphes dans Coq [Résumé long], Cécile Marcon, Cyril Allignol, Celia Picard, Blair Archibald, Michele Sevegnani, Xavier Thirioux                                           | 42 |

| Une sémantique mécanisée d'un langage FRP avec effets [Résumé long], Jordan Ischard, Frédéric Dabrowski, Jules Chouquet, Frédéric Loulergue                                                                | 46 |

| Langage Chips : Modélisation et contrôle de systèmes distribués à base de composants, <i>Anna Gallone</i>                                                                                                  | 49 |

| Session AFADL II                                                                                                                                                                                           | 53 |

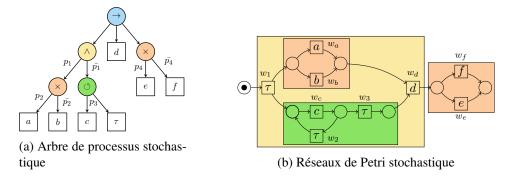

| Découverte de processus probabiliste avec des arbres de processus stochastiques [Résumé long],<br>Pierre Cry                                                                                               | 55 |

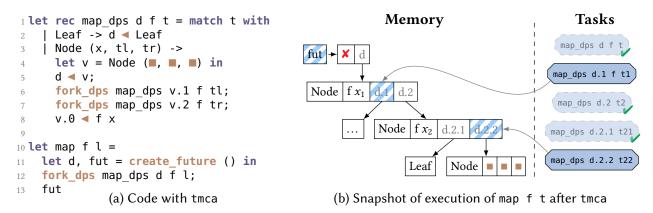

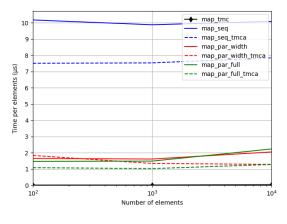

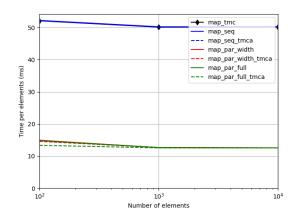

| Tail Modulo Async-Await (extended abstract), Emma Nardino, Ludovic Henrio, Gabriel Radanne, Yannick Zakowski                                                                                         | 60 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Model Checking de LTL sur Traces Finies et Infinies avec Domaines Concrets, <i>Julien Brunel, David Doose</i>                                                                                        | 65 |

| VASSAL : Verification and Analysis for Safety and Security of Applications in Life [Présentation de projet], Julien Signoles, Milan Ceska, Florian Zuleger, Tomáš Kratochvíla                        | 69 |

| Session AFADL & MTV2                                                                                                                                                                                 | 73 |

| Apprentissage et test pour les machines à états finis temporisées avec délais de sortie, <i>Evgenii Vinarskii, Natalia Kushik, Djamal Zeghlache</i>                                                  | 75 |

| Experimental evaluation of LLMs for Test Generation, Tiago Costa, Ahmad Ghandour, Mariia Soltys, Nikita Volosnikov, Yves Ledru, Nicolas Hili                                                         | 83 |

| Projet VéDySec : Vérification Dynamique de Propriétés de Sécurité, <i>Nikolai Kosmatov, Frédéric Loulergue, Julien Signoles</i>                                                                      | 91 |

| ANR RAPID VVaMIA [Présentation de projet], Frédéric Dadeau, Fabrice Bouquet, Eléa Jacquin, Dorine Tabary, Louis Lefevre, Bruno Legeard, Antoine Chevrot, Arnaud Bouzy, Bruno Besace, Fabien Lamontre | 95 |

#### **Préface**

Ces journées à Pau poursuivent les rencontres annuelles de la communauté AFADL et plus largement des groupes de recherche connexes du GDR GPL. Les journées AFADL ont pour objectif de rassembler des acteurs académiques et industriels intéressés par la mise en œuvre des techniques formelles à divers stades du développement des logiciels et/ou des systèmes. Elles visent ainsi la mise en valeur de travaux récents effectués autour de thèmes comme :

- Les techniques et outils formels contribuant à assurer un bon niveau de confiance dans la construction de logiciels et de systèmes;

- Les méthodes et processus permettant d'exploiter efficacement les techniques et outils formels disponibles ou conçus;

- Les méthodes et processus mettant en œuvre différentes techniques formelles et hétérogènes dans un développement;

- Les leçons tirées de la mise en œuvre de ces outils ou principes sur des études de cas ou des applications industrielles.

Les techniques, méthodes et outils présentés assistent notamment les activités de la modélisation, la validation et la gestion d'exigences formelles applicables aux logiciels; les spécialisations ou extensions de techniques de modélisation et d'évaluation induites par des domaines applicatifs (télécommunication, contrôlecommande, robotiques, systèmes interactifs, architectures, composition de services, applications distribuées sur le web, systèmes cyber-physiques, etc); des points de vue particuliers sur les systèmes (sécurité informatique, exécution temps réel, ...).

Sont abordés aussi dans le cadre de ces journées, le passage d'une étape de conception à la suivante : patrons de raffinement de spécifications, déploiement d'une architecture logicielle sur une architecture matérielle, génération automatique de code, réutilisation de composants, ...; test et l'évaluation rigoureuse de modèles formels ou de codes; spécification et vérification formelles d'architectures, de modèles, de programmes ou de systèmes.

Les travaux présentés s'intéressent aussi à la combinaison d'approches formelles avec des approches informelles ou semi-formelles ou à la coopération de techniques formelles de développement avec des techniques plus classiques (par exemple à la complémentarité vérification formelle / test pour les aspects V&V), aussi bien qu'à l'adaptation des approches formelles aux techniques d'apprentissage automatique et au domaine de l'informatique quantique.

Pour cette édition de 2025, le programme de AFADL a intégré des travaux spécifiquement liés aux groupes de travail : Langages et vérification de programmes (LVP) et Méthodes de test pour la validation et la vérification (MTV2) du GDR GPL lors de deux sessions communes.

Les actes sont structurés suivant les cinq sessions du programme des journées AFADL 2025 pour faciliter la consultation. Les articles présentés et listés dans les présents actes relèvent de différentes catégories, suscitées lors de l'appel à communications.

- Deux articles présentant de nouveaux travaux ou résultats de travaux académiques ou industriels non encore publiés : les articles de Vinarskii et al (page 75) et Costa et al (page 83).

- Les travaux et résultats de trois doctorantes et doctorants encadrés par les chercheuses et chercheurs de la communauté. C'est l'occasion pour les auteurs de bénéficier davantage de retours de la communauté, au delà des conseils de leur proche encadrement. Les articles suivants sont dans cette catégorie : celui de Alexandre Jean (page 16), celui d'Eléa Jacquin (page 21) et celui d'Anna Gallone (page 49).

- Des contributions présentant des projets nationaux ou internationaux : les projets VéDySec (page 91),

VVaMIA (page 95) et VASSAL (page 69).

- Des résumés d'articles récemment publiés dans des conférences internationales afin de les faire connaître

à notre communauté. Ces articles sont publiés dans les conférences suivantes: Tests and Proofs (page 5), Verification, Model Checking, and Abstract Interpretation (page 10), Fundamental Approaches to Software Engineering (page 39), Symposium on Applied Computing (pages 42 et 46), Performance Evaluation Methodologies and Tools (page 55), Object-Oriented Programming Systems, Languages, and Applications (page 60), International Conference on Formal Engineering Methods (page 65).

Il y a également trois posters spécifiques à AFADL qui seront présentés. Ces actes contiennent un résumé ainsi que le poster réduit en pages 27, 30 et 33.

Ces dix-neuf contributions proviennent de quinze établissements et laboratoires de recherche publiques de toute la France, 3 universités étrangères et quatre centres de R&D d'entreprises.

Nous remercions ici nos collègues qui ont permis et assuré le bon déroulement de ces journées : Olivier Le Goaer, Adel Noureddine et tous les collègues de Pau; Mireille Blay-Fornarino et Catherine Dubois Co-directrices du GDR Génie de la Programmation et du Logiciel; les responsables des groupes de travail MTV2 (Nikolai Kosmatov, Natalia Kushik, Pascale Le Gall, Antoine Rollet) et LVP (Nicolas Magaud, Julien Signoles); le responsable de la session poster des journées du GDR GPL Thomas Degueule.

Fabien DAGNAT, Olga KOUCHNARENKO le 10 juin 2025

### **Session AFADL I**

# Langage de spécification de contexte pour vérifier formellement des propriétés de consentement sur des modèles et du code

- Résumé long -

Myriam Clouet<sup>1</sup> Thibaud Antignac\*<sup>2</sup> Mathilde Arnaud<sup>3</sup> Julien Signoles<sup>3</sup>

<sup>1</sup> Univ. Orléans, INSA Centre Val de Loire, LIFO EA 4022

firstname.lastname@univ-orleans.fr

<sup>2</sup> CNIL (Commission nationale de l'informatique et des libertés),

3 place de Fontenoy, TSA 80715, 75334 Paris CEDEX 07, France

tantignac@cnil.fr

<sup>3</sup> Université Paris-Saclay, CEA, List, F-91120, Palaiseau, France

firstname.lastname@cea.fr

#### Résumé

Cette soumission présente l'article Context Specification Language for Formally Verifying Consent Properties on Models and Code qui a été publié à la conférence Tests and Proofs en 2023 [5]. Il porte sur la définition d'un langage formel, la formalisation de propriétés liées au consentement et à l'implémentation d'un outil de vérification formelle. Cet outil peut être utilisé soit pour vérifier une modélisation d'un système, soit pour vérifier le code correspondant à son implémentation.

#### 1 Contexte

Plusieurs domaines d'applications traitent des données personnelles, comme les sites de commerce en ligne, les assistants vocaux ou les systèmes de santé. Des lois et des régulations ont été établies autour du monde pour encadrer ces traitements, notamment le RGDP en Union Européenne. Ne pas les respecter peut mener à des amendes conséquentes, ce qui a été le cas pour Google <sup>1</sup> et WhatsApp <sup>2</sup>. Il est

<sup>\*</sup>Les vues, opinions et positions exprimées dans cet article sont celles de l'auteur et non de l'institution à laquelle il appartient. Ce travail a été réalisé en grande partie pendant que l'auteur était au CEA List.

<sup>1.</sup> https://www.lemondeinformatique.fr/actualites/lire-rgpd-google-condamne-a-50-meteuro-par-la-cnil-74062.html

$<sup>2.\</sup> https://www.lemondeinformatique.fr/actualites/lire-rgpd-whatsapp-condamne-a-225-meteuro-d-amende-84044.html$

donc crucial de vérifier qu'un système respecte des propriétés de vie privée.

Les méthodes formelles fournissent un ensemble de techniques fondées sur la logique, les mathématiques et l'informatique théorique. Elles sont utilisées pour spécifier, développer et vérifier des systèmes informatiques [7]. En particulier, elles peuvent être utiliser pour vérifier des propriétés de respect de la vie privée [8].

Une autre façon de fournir des garanties de respect de la vie privée est de suivre le principe de *protection des données dès la conception et protection des données par défaut*, qui exige que le responsable du traitement mette « en œuvre, tant au moment de la détermination des moyens du traitement qu'au moment du traitement lui-même, des mesures techniques et organisationnelles appropriées » [6]. Pour cela, le responsable du traitement doit intégrer ces mesures dès les premières étapes de développement [1]. Plus généralement, assurer qu'un système respecte la vie privée nécessite de vérifier que les propriétés de vie privée soient respectées durant tout le cycle de vie de ce système. Cela implique généralement de considérer différents niveaux d'abstraction du système (liés aux étapes du cycle de vie), ce qui complique le processus de vérification.

Les propriétés liées au consentement sont particulières car elles reposent sur un accord entre les personnes concernées par le traitement des données personnelles [4]. Ces propriétés, même si elles sont prisent en compte par les services juridiques, peuvent être parfois ignorées pendant les phases de modélisation du système et ne sont généralement pas vérifiées durant les étapes d'implémentation. Cela peut conduire à des problèmes au regard des bases légales.

#### 2 Contributions

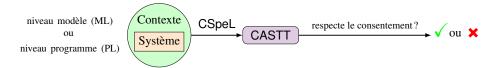

Notre article propose une approche pour vérifier des propriétés de consentement à deux étapes de développement différentes : la vérification de la modélisation et la vérification du code, comme illustré sur la figure 1. Le langage de spécification CSpeL permet aux ingénieurs de formellement spécifier les éléments à prendre en compte pour vérifier que le système respecte des propriétés de vie privée, tandis que l'outil CASTT permet de vérifier que certaines traces du modèle ou du programme sont correctes, ou encore de démontrer la correction exhaustive de l'implémentation du système vis-à-vis de ces propriétés. Nous avons évalué la correction et l'efficacité de notre approche sur des cas d'utilisations de deux domaines d'application différents, aussi bien au niveau modèle que programme.

FIGURE 1 – Vue générale de l'utilisation des contributions : CSpeL et CASTT.

Plus précisément, nos contributions sont les suivantes :

- CSpeL, un nouveau langage de spécification du contexte permettant de formaliser les éléments clés nécessaires pour vérifier deux propriétés spécifiques liées au consentement : la conformité aux finalités consenties et la conformité à la nécessité des données;

- une formalisation des deux propriétés de consentement ci-dessus, la première stipulant que les données personnelles sont seulement traitées pour des finalités de traitement consenties; et la seconde stipulant que les données personnelles sont seulement traitées lorsque cela est nécessaire.

- CASTT, un nouvel outil de vérification qui inclut :

- une méthode de vérification des propriétés précédentes sur des traces d'un modèle ou d'un programme; et

- un mécanisme de traduction de CSpeL vers le langage de spécification ACSL [3], qui permet de vérifier le respect des propriétés précédentes sur un code C à l'aide de Frama-C [2];

- une évalutation empirique de CASTT sur des cas d'utilisation pour deux domaines d'application qui illustre l'utilité de notre approche.

#### 3 Résultats

Nous avons évalués les deux mécanismes de vérification de CASTT : l'analyse de trace et la traduction pour un outil au niveau programme.

Pour le premier mécanisme, nous nous sommes intéressés aux questions de recherche suivantes :

- **RQ1** Est-ce que CASTT peut vérifier les propriétés sur une trace au niveau modèle/programme et est-ce qu'il peut détecter les traces invalides?

- **RQ2** Est-ce que CASTT est utilisable sur des grandes traces?

Pour répondre à la question **RQ1**, nous avons testé l'outil sur plusieurs exemples, aux niveaux modèle et programme, aussi bien pour des traces devant être détectées comme valides que pour des traces devant être détectées comme invalides. Nos expérimentations montrent que CASTT fourni toujours le verdict attendu.

Pour répondre à la question **RQ2**, CASTT est utilisé pour vérifier un exemple pour lequel nous faisons varier la taille de la trace (allant de 10 à 1 000 000 d'événements). Nos expérimentations montrent que le temps de vérification est linéaire par rapport à la taille de la trace et que, pour des grandes traces (avec 1 000 000 évènements), la vérification par CASTT prend moins de 4 secondes.

Pour le mécanisme de traduction, nous nous sommes intéressés aux questions de recherche suivantes :

**RQ3** Est-ce que CASTT peut vérifier des systèmes au niveau programme en traduisant un fichier CSpeL pour un outil spécifique au niveau programme, de façon à ce que cet outil puisse toujours détecter les traces invalides?

**RQ4** Est-ce que CASTT peut être utilisé sur un code de grande taille (i.e. avec beaucoup de lignes de code et d'appels de fonctions)?

Pour répondre à la question **RQ3**, nous avons testé l'outil sur des exemples variés pour lesquels nous avons vérifié si les différents greffons de vérification de Frama-C (WP poour la preuve de programmes WP, Eva pour l'interprétation, et E-ACSL pour la vérification à l'exécution) pouvaient être utilisés pour détecter les traces invalides. Nos expérimentations montrent que CASTT, combiné avec n'importe quel greffon de vérification de Frama-C, peut vérifier le respect du consentement sur le code testé.

Pour répondre à la question **RQ4**, nous testons les différentes techniques sur un même fichier C (sauf pour le nombre d'appels de fonction) et le même fichier de spécification CSpeL. Nous utilisons un générateur d'appels de fonction pour augmenter le nombre d'appels de fonctions dans la fonction main du fichier source. Les résultats de nos expérimentations montrent que le temps de génération des annotations est négligeable comparé au temps de vérification des greffons. Ils montrent également que la vérification des annotations générées ne ralentit pas exagérément le temps de vérification des greffons (généralement moins de 10% pour Eva et 5% pour E-ACSL) et plus la taille du code à vérifié est grande, moins le temps de vérification est impacté.

#### Références

- [1] Ahmadian, A.: Model-based privacy by design. Phd thesis, Universität Koblenz-Landau (2020)

- [2] Baudin, P., Bobot, F., Bühler, D., Correnson, L., Kirchner, F., Kosmatov, N., Maroneze, A., Perrelle, V., Prevosto, V., Signoles, J., et al.: The dogged pursuit of bug-free c programs: the frama-c software analysis platform. Communications of the ACM (2021)

- [3] Baudin, P., Filliâtre, J.C., Marché, C., Monate, B., Moy, Y., Prevosto, V. : ACSL : ANSI/ISO C Specification Language. Tech. rep.

- [4] Clouet, M., Antignac, T., Arnaud, M., Pedroza, G., Signoles, J.: A new generic representation for modeling privacy. In: 2022 IEEE European Symposium on Security and Privacy Workshops (EuroS&PW. pp. 203–211 (2022). https://doi.org/10.1109/EuroSPW55150.2022.00027

- [5] Clouet, M., Antignac, T., Arnaud, M., Signoles, J.: Context specification language for formally verifying consent properties on models and code. In: Tests and Proofs. pp. 68–93. Springer Nature Switzerland, Cham (2023)

- [6] European Commission: Regulation (EU) 2016/679 (General Data Protection Regulation). Tech. rep. (2016), https://eur-lex.europa.eu/legal-content/EN/TXT/PDF/?uri=CELEX:32016R0679

- [7] Huth, M., Ryan, M.: Logic in Computer Science: Modelling and Reasoning about Systems. Cambridge University Press; 2nd edition (2004)

[8] Tschantz, M.C., Wing, J.M. : Formal methods for privacy. In : International Symposium on Formal Methods (2009)

#### **Project & Conquer:**

# Élimination de quantificateurs pour la vérification de problèmes d'accessibilité dans les réseaux de Petri

Résumé long

Nicolas Amat<sup>1</sup>, Silvano Dal Zilio<sup>2</sup>, and Didier Le Botlan<sup>2</sup>

<sup>1</sup>DTIS, ONERA, Université de Toulouse, 31000, Toulouse, France <sup>2</sup>LAAS-CNRS, Université de Toulouse, CNRS, 31000, Toulouse, France

Nicolas Amat, Silvano Dal Zilio, and Didier Le Botlan. Project and Conquer: Fast Quantifier Elimination for Checking Petri Net Reachability. In *International Conference on Verification, Model Checking, and Abstract Interpretation (VMCAI)*, volume 14499 of *Lecture Notes in Computer Science*. Springer, 2024. https://laas.hal.science/hal-04375443v1

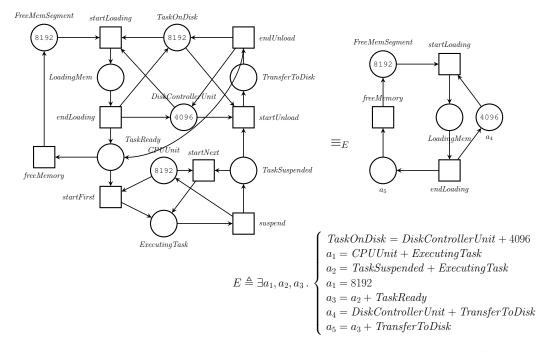

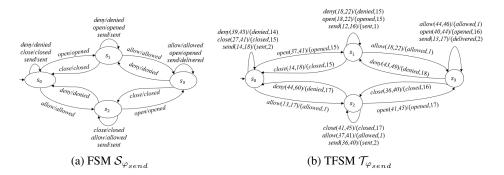

Contexte général. Dans cet article nous décrivons une méthode pour accélérer la vérification de propriétés d'accessibilité dans les réseaux de Petri en tirant parti de réductions structurelles [Ber87]. La question est de savoir si un état (aussi appelé marquage) donné ou une classe d'états décrite par un prédicat F (exprimé en utilisant une combinaison booléenne de contraintes linéaires entre le marquage des places), peut être atteint par le modèle d'un système. En prenant pour exemple un réseau de Petri représentatif de la vérification d'une architecture logicielle, qui modélise un problème de partage de ressources dans un système d'exploitation, voir la Figure 1 à gauche, on peut souhaiter vérifier s'il est possible d'atteindre un état « problématique » avec plus de tâches en cours d'exécution que de segments mémoire libres. Dans ce cas  $F \triangleq (ExecutingTask > FreeMemSegment)$ . Cette classe de formules correspond aux requêtes d'accessibilité utilisées dans le Model Checking Contest (MCC) [AAB+25], une compétition d'outils de vérification de réseaux de Petri que nous utilisons comme référence.

**Réductions polyédriques.** Cet article repose sur une approche que nous avons précédemment présentée, appelée  $réduction\ polyédrique\ [ABDZ21,ABDZ22,BLBDZ18],\ qui consiste à calculer des réductions de la forme <math>(N,E,N')$  où : N est un réseau initial que nous souhaitons analyser (dans un espace de dimension n, qui correspond au nombre de places de N); N' est un réseau résiduel, que nous espérons beaucoup plus simple que N (donc dans un espace de dimension n', inférieur à n); et E est un prédicat de Presburger (théorie du premier ordre des nombres entiers naturels munis de l'addition). L'idée est de préserver suffisamment d'informations dans E pour reconstruire l'espace d'états de N, en ne connaissant que celui de N'. En résumé, nous capturons et abstrayons l'effet des réductions en utilisant des contraintes linéaires entre les places de N et N'. Par conséquent, nous pouvons représenter l'espace d'états de N comme l'image inverse, par

E, d'un sous-ensemble de vecteurs de dimension n'. Cette technique permet, dans de nombreux cas, d'obtenir une représentation très compacte de l'espace d'états, et se traduit par une nouvelle relation d'équivalence,  $N \equiv_E N'$ , appelée *équivalence polyédrique*, en référence aux « modèles polyédriques » utilisés dans l'optimisation de programmes et l'analyse statique [Fea96, BJT99]. En effet, comme dans ces travaux, nous proposons une représentation algébrique de la relation entre un modèle et son espace d'états basée sur les ensembles de solutions de contraintes linéaires.

La contribution de notre article est une procédure d'élimination de variables quantifiées existentiellement dans l'arithmétique de Presburger, afin de projeter une propriété d'accessibilité F, sur le réseau N, en une propriété d'accessibilité F' sur le réseau réduit N', tout en préservant le verdict. Nous avons implanté cette procédure dans un nouvel outil, appelé Octant [Ama24], qui peut agir comme un pré-processeur permettant à n'importe quel model-checker de bénéficier de manière transparente de notre optimisation.

FIGURE 1 – Exemple du réseau de Petri « SmallOperatingSystem » (qui admet  $10^{17}$  marquages accessibles), provenant du Model Checking Contest et sa réduction polyédrique.

Afin d'illustrer cette approche, dans la Figure 1 nous donnons, à droite, un exemple de réduction polyédrique du réseau de gauche, avec E le prédicat Presburger permettant de lier les deux espaces d'états. Une telle abstraction est généralement obtenue en appliquant un ensemble de règles de réductions structurelles de manière itérative. Il est également intéressant de noter que notre méthode n'impose pas de restrictions sur la syntaxe des réseaux, telles que des contraintes sur les poids des arcs ou des limites sur le marquage de places. Elle peut donc s'appliquer à des réseaux non bornés (dont l'espace d'états est infini).

Conservation de l'accessibilité. Une application intéressante est le théorème de conservation de l'accessibilité [ABDZ21]: une propriété F est accessible dans N si et seulement si  $E \wedge F$  est accessible dans N'. Cette propriété est intéressante car elle signifie que nous pouvons appliquer des techniques de réduction plus agressives que, par exemple, slicing [Rak12,LOST17,KKG18], cone of influence [CGP99], ou d'autres méthodes [GRVB08,KBJ21] qui cherchent à supprimer ou à agglomérer les places qui ne sont pas pertinentes pour la propriété à vérifier (et qui ne peuvent donc pas contribuer à sa valeur de vérité). Nous ne partageons pas cette restriction dans notre approche, puisque nous réduisons les réseaux au préalable et pouvons donc réduire les places qui apparaissent dans la propriété initiale. En effet, les approches similaires au slicing ne simplifient un modèle que par rapport à une formule, alors qu'avec notre méthode, nous simplifions le modèle autant que possible et ensuite les formules si nécessaire.

Élimination de quantificateurs. Cependant, il existe une complication liée au fait que la formule  $E \wedge F$  peut inclure des variables (places) qui n'apparaissent plus dans le réseau réduit N' et qui agissent donc comme des variables existentiellement quantifiées. Cela peut compliquer certaines techniques de vérification symbolique, telles que la k-induction [SSS00] (nécessitant une quantification universelle) et empêcher l'utilisation d'approches explicites et énumératives. En effet, dans ce dernier cas, cela signifie que nous devons résoudre un problème en arithmétique linéaire entière pour chaque nouvel état visité, au lieu de simplement évaluer une formule « close ». Pour surmonter ce problème, nous proposons dans cet article une nouvelle méthode qui permet de projeter la formule  $E \wedge F$  en une formule équivalente, F', qui ne fait référence qu'aux places de N'. Ensuite, F' peut être vérifiée sur N' à l'aide de n'importe quel outil ou méthode de vérification.

Nous définissons notre projection comme une semi-procédure d'élimination des quantificateurs en arithmétique de Presburger, adaptée au type spécifique de contraintes que nous manipulons dans E. Alors que l'élimination des quantificateurs a une complexité exponentielle en général pour les formules existentielles, notre construction a une complexité linéaire et ne peut que diminuer la taille d'une formule. De plus, elle se termine toujours et renvoie un résultat dont la correction est garantie. Ce qui signifie qu'elle sous-approxime l'ensemble des modèles accessibles et que, par conséquent, un témoin de F' dans N' correspond nécessairement à un témoin de F dans N. De plus, notre méthode inclut une simple condition sur F qui suffit à détecter quand notre résultat est exact, c'est-à-dire que si F' est inaccessible dans N', alors F est inaccessible dans N. Notons que si cela n'est pas le cas, notre méthode peut, éventuellement, ne pas permettre de conclure sur l'accessibilité de F (c'est-à-dire F peut être accessible sans que F' ne le soit également). Par ailleurs, nous montrons dans évaluation expérimentale que notre projection est complète pour 80% des formules utilisées dans le MCC.

**Structure de données.** Cette procédure d'élimination de quantificateurs repose sur une nouvelle structure de données, appelée Token Flow Graph (TFG) [ADZLB21, ADZLB23], qui permet de capturer la structure particulière des contraintes apparaissant dans le prédicat Presburger (E). Les TFGs sont des graphes orientés acycliques (DAG), avec un nœud par variable apparaissant dans le prédicat E, et deux types d'arcs deux grands types de contraintes. Le premier type d'arcs correspond aux redondances, qui sont des équations de la forme  $p = q + r + \dots$  exprimant

que la place p a été supprimée et que son marquage peut être reconstruit à partir du marquage des places  $q, r, \ldots$  (voir p. ex. l'équation TaskOnDisk = DiskControllerUnit + 4096 dans la Figure 1). Le second type correspond aux agglomérations, qui sont des équations de la forme  $a = p + q + \ldots$ , générées en agglomérant plusieurs places  $(p, q, \ldots)$  en une nouvelle (a), et où le marquage de  $p, q, \ldots$  peut être reconstruit à partir de celui de a (voir p. ex. l'équation  $a_4 = DiskControllerUnit + TransferToDisk$  dans la Figure 1). Cette structure de données conduit à des algorithmes de vérification spécifiques, de complexité linéaire, en permettant de raisonner sur l'évolution des jetons dans E.

Évaluation expérimentale. Nous avons appliqué notre approche aux meilleurs outils participant au Model Checking Contest (en excluant SMPT [ADZ23] que nous développons): ITS-Tools [TM15], LoLA [Wol18] et TAPAAL [DJJ<sup>+</sup>12], sur l'ensemble des requêtes du Model Checking Contest 2023. Ce benchmark fournit un grand nombre de modèles (1 426) aux caractéristiques structurelles et comportementales variées, couvrant également une grande variété de cas d'utilisation et dont la taille varie, de 4 à 50 000 places, et de 7 à 200 000 transitions. La Table 1 résume les résultats obtenus sur l'ensemble des 897 formules difficiles (celles pour lesquelles au moins un des outils échoue) du Model Checking Contest 2023. Nos expérimentations montrent des gains de performance substantiels avec notre approche, allant de 20% à 60% en termes de requêtes supplémentaires que nous pouvons traiter (dans une limite de temps raisonnable).

| OUTILS    | # Propriéti | ÉS VÉRIFIÉES | TEMPS DE CALCUL |               |

|-----------|-------------|--------------|-----------------|---------------|

| OCTIES    | ORIGINAL    | RÉDUIT       | MOYEN           | MÉDIAN        |

| ITS-Tools | 281         | 333          | ×1.63           | ×1.04         |

| LoLA      | 188         | 241          | $\times 10.91$  | $\times 1.40$ |

| TAPAAL    | 168         | 274          | $\times 1.43$   | $\times 1.10$ |

TABLE 1 – Impact des réductions polyédriques sur les outils de l'état de l'art.

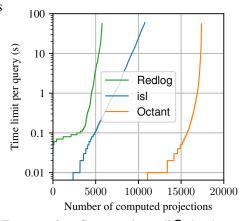

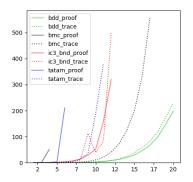

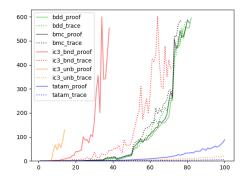

Ces résultats montrent que les réductions polyédriques sont efficaces sur un grand nombre de propriétés, orthogonales aux optimisations existantes et que leurs avantages se combinent avec d'autres optimisations. Un résultat intéressant de ce travail est la définition d'un fragment non trivial de l'arithmétique existentielle de Presburger avec de bonnes propriétés de complexité qui, nous l'espérons, pourrait être applicable dans d'autres contextes. Ce constat est appuyé par l'évaluation expérimentale représentée dans la Figure 2, où nous avons comparé, sur les requêtes du MCC, la performance d'Octant avec Redlog [DS97] et isl [Ver10], deux outils de référence pour l'arithmétique de Presburger.

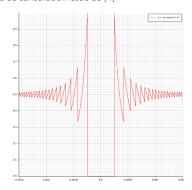

FIGURE 2 – Comparaison d'Octant avec Redlog [DS97] et isl [Ver10].

#### Références

- [AAB<sup>+</sup>25] Nicolas Amat, Elvio Amparore, Bernard Berthomieu, Pierre Bouvier, Silvano Dal Zilio, Francis Hulin-Hubard, Peter G. Jensen, Loig Jezequel, Fabrice Kordon, Shuo Li, Emmanuel Paviot-Adet, Laure Petrucci, Jiří Srba, Yann Thierry-Mieg, and Karsten Wolf. Behind the scene of the model checking contest, analysis of results from 2018 to 2023. In *TOOLympics Challenge 2023*. Springer, 2025. doi:10.1007/978-3-031-67695-6\_3.

- [ABDZ21] Nicolas Amat, Bernard Berthomieu, and Silvano Dal Zilio. On the Combination of Polyhedral Abstraction and SMT-Based Model Checking for Petri Nets. In *Application and Theory of Petri Nets and Concurrency (PETRI NETS)*, volume 12734 of *Lecture Notes in Computer Science*. Springer, 2021. doi:10.1007/978-3-030-76983-3-9.

- [ABDZ22] Nicolas Amat, Bernard Berthomieu, and Silvano Dal Zilio. A Polyhedral Abstraction for Petri Nets and its Application to SMT-Based Model Checking. *Fundamenta Informaticae*, 187(2-4):103–138, 2022. doi:10.3233/FI-222134.

- [ADZ23] Nicolas Amat and Silvano Dal Zilio. SMPT: A Testbed for Reachabilty Methods in Generalized Petri Nets. In *Formal Methods (FM)*, volume 14000 of *Lecture Notes in Computer Science*. Springer, 2023. doi:10.1007/978-3-031-27481-7-25.

- [ADZLB21] Nicolas Amat, Silvano Dal Zilio, and Didier Le Botlan. Accelerating the Computation of Dead and Concurrent Places Using Reductions. In *Model Checking Software (SPIN)*, volume 12864 of *Lecture Notes in Computer Science*. Springer, 2021. doi:10.1007/978-3-030-84629-9\_3.

- [ADZLB23] Nicolas Amat, Silvano Dal Zilio, and Didier Le Botlan. Leveraging polyhedral reductions for solving Petri net reachability problems. *International Journal on Software Tools for Technology Transfer*, 25(1):95–114, 2023. doi:10.1007/s10009-022-00694-8.

- [Ama24] Nicolas Amat. Octant : The Reachability Formula Projector. un outil pour projeter des propriétés d'accessibilité d'un réseaux de petri sur sa version réduite, 2024. URL: https://github.com/nicolasAmat/Octant.

- [Ber87] G. Berthelot. Transformations and Decompositions of Nets. In *Petri Nets: Central Models and Their Properties (ACPN)*, volume 254 of *Lecture Notes in Computer Science*. Springer, 1987. doi:10.1007/978-3-540-47919-2\_13.

- [BJT99] Frédéric Besson, Thomas Jensen, and Jean-Pierre Talpin. Polyhedral analysis for synchronous languages. In *Static Analysis (SAS)*, volume 1694 of *Lecture Notes in Computer Science*. Springer, 1999. doi:10.1007/3-540-48294-6\_4.

- [BLBDZ18] Bernard Berthomieu, Didier Le Botlan, and Silvano Dal Zilio. Petri net Reductions for Counting Markings. In *Model Checking Software (SPIN)*, volume 10869 of *Lecture Notes in Computer Science*. Springer, 2018. doi:10.1007/978-3-319-94111-0\_4.

- [CGP99] E. M. Clarke, Orna Grumberg, and Doron Peled. *Model Checking*. MIT Press, 1999.

- [DJJ<sup>+</sup>12] Alexandre David, Lasse Jacobsen, Morten Jacobsen, Kenneth Yrke Jørgensen, Mikael H. Møller, and Jiří Srba. TAPAAL 2.0: Integrated Development Environment for Timed-Arc Petri Nets. In *Tools and Algorithms for the Construction and Analysis of Systems (TACAS)*, volume 7214 of *Lecture Notes in Computer Science*. Springer, 2012. doi:10.1007/978-3-642-28756-5\_36.

- [DS97] Andreas Dolzmann and Thomas Sturm. Redlog: computer algebra meets computer logic. *ACM SIGMA Bulletin*, 31(2):2–9, 1997. doi:10.1145/261320.261324.

- [Fea96] Paul Feautrier. Automatic parallelization in the polytope model. In *The Data Parallel Programming Model*, volume 1132 of *Lecture Notes in Computer Science*. Springer, 1996. doi:10.1007/3-540-61736-1\_44.

- [GRVB08] Pierre Ganty, Jean-François Raskin, and Laurent Van Begin. From many places to few: Automatic abstraction refinement for petri nets. *Fundamenta Informaticae*, 88(3):275–305, 2008.

- [KBJ21] Jiawen Kang, Yunjun Bai, and Li Jiao. Abstraction-Based Incremental Inductive Coverability for Petri Nets. In *Application and Theory of Petri Nets and Concurrency (PETRI NETS)*, volume 12734 of *Lecture Notes in Computer Science*. Springer, 2021. doi:10.1007/978-3-030-76983-3\_19.

- [KKG18] Yasir Imtiaz Khan, Alexandros Konios, and Nicolas Guelfi. A survey of Petri nets slicing. *ACM Computing Surveys*, 51(5):1–32, 2018. doi:10.1145/3241736.

- [LOST17] Marisa Llorens, Javier Oliver, Josep Silva, and Salvador Tamarit. An integrated environment for Petri net slicing. In *Application and Theory of Petri Nets and Concurrency (PETRI NETS)*, volume 10258 of *Lecture Notes in Computer Science*. Springer, 2017. doi:10.1007/978-3-319-57861-3\_8.

- [Rak12] Astrid Rakow. Safety slicing Petri nets. In Application and Theory of Petri Nets and Concurrency (PETRI NETS), volume 7347 of Lecture Notes in Computer Science. Springer, 2012. doi:10.1007/978-3-642-31131-4-15.

- [SSS00] Mary Sheeran, Satnam Singh, and Gunnar Stålmarck. Checking Safety Properties Using Induction and a SAT-Solver. In *Formal Methods in Computer-Aided Design* (FMCAD), volume 1954 of Lecture Notes in Computer Science. Springer, 2000. doi:10.1007/3-540-40922-X\_8.

- [TM15] Yann Thierry-Mieg. Symbolic Model-Checking Using ITS-Tools. In *Tools and Algorithms for the Construction and Analysis of Systems (TACAS)*, volume 9035 of *Lecture Notes in Computer Science*. Springer, 2015. doi:10.1007/978-3-662-46681-0\_20.

- [Ver10] Sven Verdoolaege. isl: An integer set library for the polyhedral model. In *Mathematical Software (ICMS)*, volume 6327 of *Lecture Notes in Computer Science*. Springer, 2010. doi:10.1007/978-3-642-15582-6\_49.

- [Wol18] Karsten Wolf. Petri Net Model Checking with LoLA 2. In Application and Theory of Petri Nets and Concurrency (PETRI NETS), volume 10877 of Lecture Notes in Computer Science. Springer, 2018. doi:10.1007/978-3-319-91268-4\_18.

#### Transformations automatisées de preuves Coq

Alexandre Jean, Nicolas Magaud\*

Lab. ICube UMR 7357 CNRS Université de Strasbourg, France

#### Résumé

Les assistants de preuves interactifs tels que Coq [10] permettent à leurs utilisateurs d'écrire et de vérifier des preuves sur des sujets variés. Dans cette thèse, nous explorons le cycle de vie d'une preuve Coq après son écriture, notamment la phase de maintenance mais aussi les différentes réécritures possibles de cette preuve. Dans cet objectif, nous présentons dans ce document nos travaux actuels consistant en une bibliothèque de réécriture et d'exécution d'arbre de syntaxe abstraite (AST) Coq ainsi qu'un exemple de transformation réalisable à l'aide de cette bibliothèque.

Mot clés: assistant de preuve interactif, ingénierie de la preuve, refactoring de preuve.

#### 1 Introduction

L'objectif principal d'une preuve écrite dans un assistant de preuve interactif est de vérifier que la propriété énoncée est correcte. Dans le reste de ce document, on s'intéressera aux preuves dans le langage Coq. On s'intéresse aux transformations possibles d'une preuve après sa validation comme correcte. Transformer une preuve consiste à effectuer une suite d'opérations ajoutant, remplaçant ou supprimant des nœuds de la preuve. Chaque nœud correspond à une "phrase" dans la grammaire Coq, c'est-à-dire une commande ou tactique se terminant par un point.

Des exemples possibles de ces transformations sont la suppression des tactiques et commandes non nécessaires à la complétion de la preuve telles que des commandes Search ou des tactiques de simplification superflues tel que simpl. On peut aussi vouloir ajouter des éléments de structure à la preuve pour par exemple l'indenter à l'aide de bullets. Un exemple de transformation utilisant des remplacements de nœuds est une transformation remplaçant chaque appel à la tactique intros par intros  $V_1$   $V_2$  ...  $V_n$  avec V, la liste des variables introduites par intros. Cette transformation permet de rendre le script de preuve plus robuste, car il n'est alors plus dépendant de l'algorithme de nommage des variables de Coq.

Il est aussi possible de combiner ces différentes méthodes de transformation, par exemple en remplaçant les commandes de recherche de preuve telles que *auto* par les étapes effectuées par *auto*. Bien qu'il soit possible de réaliser ces transformations manuellement, elles peuvent être longues et fastidieuses dans le cas de grands développements et il est possible de les automatiser.

Il existe plusieurs implémentations de transformations spécifiques dans la littérature. On trouve notamment une transformation permettant de passer d'une preuve utilisant plusieurs tactiques et commandes à une preuve n'en contenant qu'une seule, en combinant les tactiques à l'aide des *tacticals*; et [] de Coq [8]. À l'inverse, une transformation visant à décomposer une telle preuve en une séquence de tactiques élémentaires a également été proposée, avec deux implémentations distinctes: l'une par Magaud *et al.* [7], et l'autre par Shi *et al.* [9].

Ces implémentations ne sont que des prototypes spécialisés dans un type de transformation. Afin de faciliter la réalisation d'un plus grand nombre de transformations, nous avons développé une bibliothèque pour l'écriture et l'exécution d'arbres de syntaxe abstraite (AST) de Coq.

<sup>\*. {</sup>alexandre.jean,magaud}@unistra.fr

<sup>1.</sup> Désormais nommé Rocq depuis la version 9.0.0

#### 2 Bibliothèque de réécriture d'AST

Afin de pouvoir réaliser ces transformations, le premier développement de cette thèse consiste en la réalisation d'une bibliothèque de réécriture d'AST Coq. Cette bibliothèque s'appuie sur la bibliothèque coq-lsp [5] pour extraire l'AST d'un fichier Coq. Une fois cet AST obtenu, on note L la liste de nœuds syntaxiques situés à la profondeur zéro de l'AST auxquels on associe leur position dans le document et un identifiant unique.

Une fois la liste L récupérée, nous avons implémenté une méthode permettant de récupérer la liste des preuves P présentes dans un document. Une preuve est ici définie comme une structure composée du nœud de la propriété à démontrer, ainsi que d'une liste de nœuds contenant les commandes et tactiques utilisées pour prouver cette propriété.

| Preuve en Coq                                                          | Arbre de Preuve                                       |

|------------------------------------------------------------------------|-------------------------------------------------------|

|                                                                        | Lemma add_zero:                                       |

| <pre>Lemma add_zero: forall n : nat, n + 0 = n.</pre>                  | $\forall n \in nat, n+0 = n$                          |

| Proof. induction n. reflexivity. simpl. rewrite IHn. reflexivity. Qed. | Proof.    induction n  reflexivity simpl  rewrite IHn |

|                                                                        | reflexivity                                           |

TAB. 1 – Preuve et arbre de preuve de add\_zero

Ces preuves peuvent ensuite être transformées à l'aide de notre bibliothèque en arbre de preuve.

Un arbre de preuve T est défini comme l'arbre dont les nœuds correspondent à ceux d'une preuve p, et qui satisfait les conditions suivantes: la racine de l'arbre représente la propriété démontrée par la preuve p; chaque nœud possède un nombre d'enfants égal au nombre de sous-buts générés par la tactique qui lui est associée et chaque nœud admet pour parent le nœud contenant soit la tactique l'ayant créée, soit la tactique dont l'état final constitue l'état initial du nœud. Un exemple d'une preuve et de son arbre de preuve correspondant est présenté dans la table 1.

Nous avons en parallèle défini des méthodes de transformation d'AST qui permettent de supprimer, remplacer ou ajouter des nœuds dans une preuve, un arbre de preuve ou un document L en déplaçant automatiquement les autres nœuds dans des positions valides. En utilisant ces définitions, on définit de manière formelle une transformation de preuve comme vu au paragraphe précédent comme une fonction f prenant en argument une preuve ou un arbre de preuve et renvoyant une liste d'étapes de transformation correspondant aux étapes de la transformation parmi l'ensemble d'opérations suivant:

```

\{Remove(id), Replace(id, new\_node), Add(new\_node)\}.

```

Ici, l'opération Remove(id) supprime le nœud avec l'identifiant id, l'opération  $Replace(id,new\_node)$  le remplace par  $new\_node$  et l'opération  $Add(new\_node)$  ajoute  $new\_node$ .

Les transformations renvoient une liste d'étapes de transformation à la place d'une nouvelle preuve afin de bénéficier des avantages du patron de conception commande, notamment la possibilité de traiter une transformation comme une transaction réversible ainsi que de bénéficier d'un debugging plus granulaire.

#### 3 Exemple d'une transformation automatisée

Afin de présenter l'intérêt ainsi que les capacités actuelles de notre outil de transformation de preuve, nous présentons ici la transformation d'une preuve contenant des appels à la tactique *auto* en une preuve remplaçant les appels à cette tactique par la liste des tactiques trouvées par chaque *auto*. Nous prenons comme exemple, la preuve suivante:

```

Goal forall P Q R S : Prop,

(P -> Q) -> (Q -> R) -> (R -> S) -> (P \/ S) -> (Q \/ R \/ S).

Proof.

intros P Q R S HPQ QRR RSS H.

destruct H.

auto.

right; right.

assumption.

Qed.

```

Selon la documentation Coq, il est possible d'obtenir la liste des étapes utilisées par *auto* en utilisant la tactique *info\_auto*. La première étape de la transformation consiste donc à exécuter la tactique *info\_auto* à chaque nœud contenant la tactique *auto*.

Cette tactique renvoie une chaîne de caractères C représentant la recherche effectuée par la tactique auto composée d'une liste éventuelle de tactique intro, suivi d'un arbre de recherche de preuve. Dans notre exemple, on obtient la sortie C suivante:

Listing 1: Sortie de la commande info\_auto

```

(* info auto: *)

1

simple apply or_intror (in core).

2

simple apply or_intror (in core).

3

simple apply RSS.

4

simple apply QRR.

5

simple apply HPQ.

6

7

simple apply or_introl (in core).

8

simple apply QRR.

9

simple apply HPQ.

assumption.

10

```

Cet arbre contient la liste des tactiques de la preuve trouvée par *auto* ainsi que les tentatives infructueuses de recherche qui devront être éliminées par l'algorithme. Dans le cas d'une recherche infructueuse, cet arbre contiendra un seul nœud contenant la tactique *idtac*.

Les nœuds de cet arbre ont une profondeur égale au nombre d'espaces précédant leur représentation sur leur ligne dans C. Le parent de chaque nœud n est le premier nœud précédent dont la profondeur est égal à la profondeur du nœud n moins un.

Une fois cette chaîne de caractères convertie en une liste de tactique intro (ici vide) et un arbre n-aire de recherche S, l'algorithme décrit ci-dessous est exécuté sur S pour obtenir la liste des étapes effectives permettant de remplacer la tactique auto.

On applique une réduction en profondeur sur l'arbre de recherche. Ici l'accumulateur de la réduction correspond à une pile P de tuples  $t=(t_n,t_s,t_{depth},t_{child\_count},t_{goal\_count},t_{r?})$  dont chaque élément contient le nœud précédent  $t_n$ , l'état précédent de ce nœud  $t_s$ , sa profondeur précédente  $t_{depth}$ , son nombre d'enfants  $t_{child\_count}$ , son nombre de buts  $t_{goal\_count}$  ainsi qu'une valeur booléenne indiquant si l'exécution du nœud a réussi à réduire le nombre de buts  $t_{r?}$ .

A la sortie de l'algorithme, la pile P contient une liste de tuples dont les éléments  $t_n$  représentent dans l'ordre inverse les étapes de la preuve effectuées par auto.

Au début de chaque itération k de la réduction, on récupère le nœud courant  $n_k$  ainsi le sommet de P qu'on nomme s. Si s a une profondeur  $s_{depth}$  supérieure a celle du nœud actuel, on dépile P jusqu'à

| $\overline{t_n}$       | $t_{ m depth}$ | $t_{ m child\_count}$ | $t_{ m goal\_count}$ | $t_{r?}$ |

|------------------------|----------------|-----------------------|----------------------|----------|

| assumption             | 5              | 0                     | 1                    | true     |

| simple apply HPQ       | 4              | 1                     | 2                    | false    |

| simple apply QRR       | 3              | 1                     | 2                    | false    |

| simple apply or_introl | 2              | 1                     | 2                    | false    |

| simple apply or_intror | 1              | 2                     | 2                    | false    |

TAB.  $2 - Pile\ P\ t = (t_n,\_,t_{depth},t_{child\_count},t_{goal\_count},t_{r?})$  après l'exécution de l'algorithme. On ignore  $t_s$  non représentable.

ce que le sommet de la pile corresponde à un nœud avec une profondeur inférieure ou à un nœud ayant réduit le nombre de buts. Cette opération élimine les branches de recherche inutiles précédentes et ce nœud est ensuite utilisé en remplacement de s pour la suite de l'itération.

On exécute ensuite  $n_k$  à partir de l'état précèdent  $s_s$ . Puis, on vérifie si le nœud courant  $n_k$  a des enfants. Si oui, alors on l'ajoute à la pile P. Sinon, on considère ce nœud comme terminal. Dans ce cas on vérifie si après l'exécution de  $n_k$  le nombre de but courant diminue. Si oui, alors on l'ajoute à P avec l'indicateur qu'il a réduit le nombre de buts. Sinon on élimine la branche de recherche de ce nœud en dépilant P jusqu'à arriver sur un nœud avec plusieurs enfants.

Une fois la réduction appliquée sur tous les nœuds de l'arbre de recherche, on récupère la liste de tactiques depuis P (Table 2) et on assigne à chaque nœud une position dans la preuve. Le résultat de l'application de cet algorithme sur la preuve servant d'exemple est le suivant:

```

simple apply or_intror.

simple apply or_introl.

simple apply QRR.

simple apply HPQ.

assumption.

```

On en déduit que la première branche (lignes 3-6) du listing 1 de la recherche initiale a été éliminée car un seul nœud a réduit le nombre de buts dans la Table 2, à savoir le nœud *assumption*.

#### 4 Conclusion

Cet article décrit notre approche pour la transformation automatique de preuve Coq. Nous avons décrit les différentes structures actuelles que nous utilisons pour représenter une preuve ainsi qu'un exemple d'une transformation possible sur une preuve. Par la suite, nous souhaitons explorer d'autre formes de représentation de preuve telles que les *Hiproofs* [4] ainsi que d'autres transformations plus complexes telle que la constructivisation [1] de l'arithmétisation [3] de la géométrie de Tarski formellement vérifiée dans la bibliothèque GeoCoq [2]. Afin de pouvoir traiter de larges bibliothèques, nous développons un outil de traitement de tous les fichiers d'une bibliothèque en suivant l'ordre des dépendances. Cela nous permettra, à terme, d'évaluer notre outil et certaines transformations sur des bibliothèques telles que la bibliothèque standard de Coq, la bibliothèque de géométrie GeoCoq ou le compilateur certifié CompCert [6] .

#### Références

- [1] Michael Beeson. A Constructive Version of Tarski's Geometry. *Annals of Pure and Applied Logic*, 166(11):1199–1273, 2015.

- [2] Michael Beeson, Pierre Boutry, Gabriel Braun, Charly Gries, and Julien Narboux. GeoCoq, June 2018.

- [3] Pierre Boutry, Gabriel Braun, and Julien Narboux. Formalization of the Arithmetization of Euclidean Plane Geometry and Applications. *Journal of Symbolic Computation*, 90:149–168, 2019.

- [4] Ewen Denney, John Power, and Konstantinos Tourlas. Hiproofs: A Hierarchical Notion of Proof Tree. *Electr. Notes Theor. Comput. Sci.*, 155:341–359, 05 2006.

- [5] Emilio Jesús Gallego Arias, Ali Caglayan, Shachar Itzhaky, Fréderic Blanqui, Rodolphe Lepigre, et al. rocq-lsp: a Language Server for the Rocq Prover, 2025.

- [6] Xavier Leroy. Formal Verification of a Realistic Compiler. *Commun. ACM*, 52(7):107–115, July 2009.

- [7] Titouan Lozac'h and Nicolas Magaud. Post-processing Coq Proof Scripts to Make Them More Robust. In 2nd Workshop on the development, maintenance, refactoring and search of large libraries of proofs, September 13-14, 2024, Tbilissi, Georgia, 2024.

- [8] Nicolas Magaud. Towards Automatic Transformations of Coq Proof Scripts. In *Automated Deduction in Geometry (ADG 2023)*, Belgrade, Serbia, November 2023. Pedro Quaresma et Kovács Zoltán.

- [9] Jessica Shi, Cassia Torczon, Harrison Goldstein, Andrew Head, and Benjamin Pierce. Designing Proof Deautomation in Rocq. In *Proceedings of the 15th Workshop on Evaluation and Usability of Programming Languages and Tools (PLATEAU)*, 2025.

- [10] The Coq Development Team. The Coq Proof Assistant.

## Approche neuro-symbolique pour générer un référentiel de test \*

Eléa Jacquin

Université Marie et Louis Pasteur, CNRS, institut FEMTO-ST

F-25030 Besançon, France

elea.jacquin@femto-st.fr

#### Résumé

Ce papier présente l'application de méthodes neuro-symboliques pour automatiser la génération de tests logiciels en combinant les capacités d'interprétation sémantique des Large Language Models (LLMs) avec la rigueur formelle des méthodes symboliques. Ce travail sera appliqué dans le cadre du projet ANR VVaMIA qui a démarré début 2025.

Mots-clés: tests logiciels, intelligence artificielle, neuro-symbolique

#### 1 Introduction

Les tests sont une partie cruciale du cycle de développement des logiciels. Ils augmentent la confiance envers le système sous test [1]. Dans des domaines critiques tels que l'aéronautique, la santé ou les systèmes embarqués, leur importance devient encore plus cruciale, puisque le moindre défaut peut avoir des conséquences catastrophiques [2].

L'écriture manuelle des tests est un exercice long et rigoureux : il est donc courant de faire des erreurs, surtout si le système sous test est complexe. Apporter des éléments pour accompagner les ingénieurs validation dans la conception et la gestion d'un patrimoine de test serait une véritable aide.

L'équipe VESONTIO du département informatique du laboratoire FEMTO-ST, où ces travaux sont réalisés, possède une expertise de plus de 20 ans dans le Model-Based Testing (MBT), couvrant à la fois les aspects théoriques et appliqués. Une des limites qui freine l'adoption de cette technique est la conception du modèle. En effet, cela demande beaucoup de temps, nécessite une bonne compréhension des besoins du système, des langages de modélisation et une expertise métier du domaine d'application du système.

L'utilisation d'Intelligences Artificielles (IAs) génératives pourrait constituer une solution pour atténuer cette difficulté. L'arrivée récente des grands modèles

<sup>\*</sup>Encadrée par Fabrice Bouquet, Frédéric Dadeau et Dorine Tabary au DISC/FEMTO-ST.

de langage (LLMs) a ouvert une nouvelle approche de génération de tests par leur réflexion plus humaine sur le langage naturel [3, 4]. Dans le domaine de l'ingénierie des exigences, les techniques de Traitement du Langage Naturel (NLP), incluant les LLMs, sont utilisées pour extraire des exigences à partir de cahiers des charges. Cependant, leur principal inconvénient réside dans leur tendance aux hallucinations et leur manque de fiabilité absolue [5].

#### 2 Approche proposée

Le processus classique de génération de tests évolue progressivement d'un langage naturel avec le cahier des charges, les exigences et les scénarios vers un langage de programmation exécutable avec les tests symboliques (scripts de tests où les données ne sont pas encore définies) et les scripts exécutables.

Ce déroulement présente deux défis majeurs : l'interprétation des spécifications ambiguës en langage naturel et la production d'un code de test valide. En effet, bien que riche en connaissance métier, le cahier des charges présente souvent des ambiguïtés sémantiques ou des exigences métiers implicites, ce qui complexifie son traitement automatique avec les techniques traditionnelles de NLP. Au contraire, la traduction de ces exigences en tests formels exige une rigueur mathématique généralement incompatible avec les approximations tolérées en langage naturel. Ainsi, un couplage avec de l'IA symbolique, qui elle utilise des langages formels comme la logique, permettrait d'obtenir des valeurs attendues avec une plus grande confiance. Dans la littérature, cette méthode est qualifiée de neuro-symbolique [6, 7].

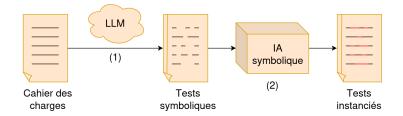

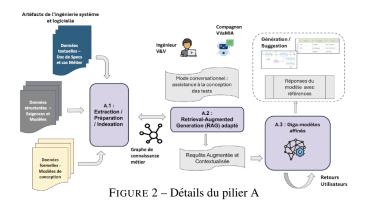

L'approche neuro-symbolique, illustrée dans la figure 1, propose une réponse à ces défis en combinant :

- l'IA générative pour l'analyse des documents initiaux (transition cahier des charges vers exigences par exemple)

- Des méthodes symboliques pour la génération de tests exécutables (transition tests symboliques vers tests instanciés)

FIGURE 1 – Processus de génération de tests

Le passage direct du cahier des charges aux tests symboliques présente des risques majeurs lorsqu'il est entièrement confié à des LLMs : hallucinations, absence de traçabilité et faible confiance dans les résultats. Ces limitations nous ont conduits à développer une méthodologie plus robuste et contrôlée.

Notre approche consiste à décomposer le processus global en une série d'étapes intermédiaires vérifiables. Plutôt que de tenter une transformation directe du cahier des charges vers des tests exécutables, nous introduisons différentes phases : extraction structurée des exigences, création d'un modèle du système, génération de scénarios de test et production de tests exécutables par exemple.

Cette granularité apporte plusieurs bénéfices. D'une part, elle permet un meilleur contrôle qualité à chaque niveau d'abstraction. D'autre part, elle offre une traçabilité complète entre les différents artefacts produits. Enfin, elle autorise des interventions correctives lorsqu'une erreur est détectée, bien avant la phase finale.

Les avantages majeurs de cette approche sont qu'elle est une assistance précieuse pour l'ingénieur validation, puisqu'elle lui donne le contrôle sur ce qui est produit à chaque étape du processus et donc assure une traçabilité des résultats.

#### 3 Premiers résultats

Une étude comparative sur les LLMs les plus utilisés sur l'extraction d'exigences depuis un cahier des charges a été réalisée. Cette étape est critique dans le processus puisqu'elle est la première donc s'il y a une mauvaise interprétation des fonctionnalités attendues dans le système, les tests produits à la fin seront erronés.

Pour effectuer cette étude, il faut constituer le meilleur prompt possible pour maximiser les résultats. Après une recherche sur les différentes techniques d'ingénierie des prompts, la stratégie adoptée est d'utiliser du zero-shot prompting (pas d'exemple donné) et la décomposition de la demande en cinq parties :

- Rôle: Définit le contexte et le niveau d'expertise attendu

- Instruction : Spécifie l'action précise à réaliser

- Contraintes : Fixe les règles et limitations impératives

- Format : Détermine l'organisation de la sortie

- **Données** : Fournit le matériel source à traiter

Aucun LLM n'a proposé d'exigences ne respectant pas le cahier des charges avec cette stratégie. Avec un prompt simple, les résultats sont plus créatifs donc plus à même de ne pas respecter strictement le cahier des charges.

L'expérience a été réalisée avec deux cahiers des charges en anglais. Une liste d'exigences de ceux-ci a été conçue manuellement par une personne experte dans le domaine du test et en comptabilise 32.

Les résultats de l'expérience montrent que, sur 10 générations, ChatGPT excellent en générant en moyenne 94,1% des exigences de la liste, suivi de DeepSeek-V3 avec 90,6%. Juste après, Claude a un score de 87,8%, Mistral 84,1%, Qwen 82,2% et en dernier DeepSeek-R1 avec 63,1%.

Ces résultats, bien qu'indicatifs, ne reflètent qu'une facette des capacités des différents LLMs évalués. Une analyse plus fine révèle des différences significatives dans leur mode de fonctionnement : par exemple, Mistral à beaucoup plus de mal à produire des exigences atomiques que Qwen.

Nous nous sommes donc interessés aux métriques existantes sur l'extraction

d'exigences et avons remarqué qu'elles avaient des failles et qu'elles n'étaient pas pertinentes pour montrer les capacités réelles des LLMs. Nous avons donc cherché à en définir de nouvelles comme par exemple évaluer l'atomicité des exigences, leur cohérence avec le cahier des charges ou leur exhaustivité.

#### 4 Suite des travaux

Par la suite, nous envisageons de produire avec l'aide de LLMs des modèles à partir d'exigences, puis des scénarios depuis un modèle et des exigences pour pouvoir ensuite comparer leur qualité avec ceux obtenus par production directe depuis des exigences. Une autre question soulevée est la définition et l'instanciation de données concrètes pour pouvoir configurer des tests exécutables.

Les travaux de cette thèse seront appliqués dans le projet ANR RAPID VVa-MIA. Il est porté par l'entreprise Smartesting Solution & Services et inclus dans son consortium Thalès LAS ainsi que FEMTO-ST. Il s'intéresse au couplage entre l'IA générative et les modèles, dans le contexte de la vérification et la validation de systèmes embarqués en utilisant des tests logiciels. Ce projet vise à la production d'assistants IA facilitant les tâches de conception et de maintenance des tests logiciels.

#### Références

- [1] G. Myers, *The Art of Software Testing*. Business Data Processing: A Wiley Series, Wiley, 1979.

- [2] T. Huckle and T. Neckel, *Bits and Bugs : A Scientific and Historical Review of Software Failures in Computational Science*. Society for Industrial and Applied Mathematics, 2019.

- [3] J. Wang, Y. Huang, C. Chen, Z. Liu, S. Wang, and Q. Wang, "Software testing with large language models: Survey, landscape, and vision," *IEEE Transactions on Software Engineering*, 2024.

- [4] R. Feldt, S. Kang, J. Yoon, and S. Yoo, "Towards autonomous testing agents via conversational large language models," in *IEEE/ACM International Conference on Automated Software Engineering (ASE)*, 2023.

- [5] N. Maleki, B. Padmanabhan, and K. Dutta, "Ai hallucinations: A misnomer worth clarifying," in *IEEE Conference on Artificial Intelligence (CAI)*, 2024.

- [6] B. P. Bhuyan, A. Ramdane-Cherif, R. Tomar, and T. P. Singh, "Neuro-symbolic artificial intelligence: a survey," *Neural Computing and Applications*, 2024.

- [7] Z. Wan, C.-K. Liu, H. Yang, C. Li, H. You, Y. Fu, C. Wan, T. Krishna, Y. Lin, and A. Raychowdhury, "Towards cognitive ai systems: a survey and prospective on neuro-symbolic ai," 2024. arXiv:2401.01040 [cs].

### **Session poster AFADL**

## On the use of generalisation and unification for composing interactions via gate connection

Joel Nguetoum Kenne<sup>1</sup>, Boutheina Bannour<sup>2</sup>, and Pascale Le Gall<sup>3</sup>

- <sup>1</sup> Université Paris-Saclay, CEA, List, F-91120, Palaiseau, France christian.nguetoumkenne@cea.fr

- <sup>2</sup> Université Paris-Saclay, CEA, List, F-91120, Palaiseau, France boutheina.bannour@cea.fr

- <sup>3</sup> Université Paris-Saclay, CentraleSupélec, MICS Fr-91192 Gif-sur-Yvette Cedex, France. pascale.legall@centralesupelec.fr

A Distributed System (DS) is a collection of concurrently operating subsystems communicating via message exchange. Formal specifications of DSs are crucial for tasks such as runtime verification, model-based testing or system assembly during design. We utilise Interaction Language (IL), a formalism for the formal specification of DSs, which is based on an algebra of terms. These terms are constructed from atomic interactions, including the empty interaction, message passing between subsystems, and actions, which can be message emissions or receptions that define the communication of a subsystem with its environment. These atomic interactions are temporally structured using scheduling operators, which include weak sequencing, concurrency, alternative behaviour and repetition, adhering to algebraic laws such as associativity and commutativity, grounded in their formal semantics. The IL features a graphical representation akin to UML Sequence Diagrams or Message Sequence Charts.

To obtain an interaction specification of a given DS, one can either directly design a global interaction model of the entire system, which might not detail the inner workings of the local subsystems. Or we can independently model each subsystem with a local interaction model and derive the global model through composition. Our work aims to develop an algorithmic method for composing local interaction models.

In local models, an emission of a message to the environment paired with the reception of the same message in another local model is termed complementary actions, linked by a shared object called a gate. Our approach to the composition of local interactions involves glueing complementary actions into message passing within a composite model, employing equational unification and generalisation. Equational generalisation identifies commonalities between terms, while equational unification finds substitutions that equate terms modulo equations.

Our approach to interaction composition leverages generalisation and unification techniques, preprocessing terms to highlight shared gates and obscure irrelevant sub-interactions, thereby inherently utilising the algebraic properties of scheduling operators. Future work will focus on exploring computational aspects.

# On the use of generalisation and unification for composing interactions via gate connection

Christian Joel Kenne Nguetoum<sup>1,2</sup> christian.nguetoumkenne@cea.fr

#### Advisors: Pascale Le Gall <sup>1</sup>, Boutheina Bannour<sup>2</sup>

1 Université Paris-Saclay, CentraleSupélec, Laboratoire de Mathématiques et d'Informatique pour la Complexité et les Systèmes (MICS), 91192 Gif-Sur-Yvette, France

#### 2 CEA Paris Saclay, Centre Nano-Innov, Laboratoire d'Exigences et de Conformité des Systèmes(LECS), 91120 Palaiseau, France

#### Interaction models with gates

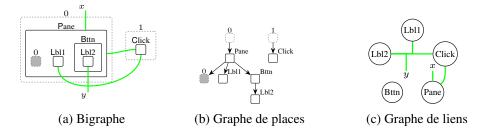

We use the Interaction Language [1] to specify distributed systems. In addition to its algebraic structure, it provides an easy-to-read, diagrammatic notation similar to MSCs and UML Sequence Diagrams.

Each subsystem is represented by a vertical line called a **lifeline**, with message exchanges shown as horizontal arrows between lifelines. The language includes scheduling operators to express complex behaviours: **vp** for message passing, **loop** for repetition, **par** for concurrency, **alt** for choice, and **seq** for weak sequencing.

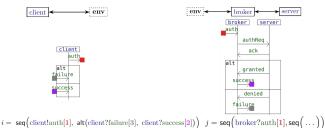

Actions correspond to message emissions (outgoing arrows) and receptions (incoming arrows), specifying communication with the environment (env). When an emission in one model and a reception in another refer to the same message, they are called complementary actions. Such actions are linked via a shared object known as a gate. In the example below, the emission of the message auth by the lifeline client ( clientlauth[1] in model i) and its reception by broker ( broker?auth[1] in model j) are complementary and share the gate 1.

The operators obey algebraic laws grounded in the formal semantics [1] of the language.

| Property                   | Operator                                       | Equation                                                 |

|----------------------------|------------------------------------------------|----------------------------------------------------------|

| Associativity              | $f \in \{\text{seq}, \text{par}, \text{alt}\}$ | $f(f(x,y),z) \approx f(x,f(y,z))$                        |

| Commutativity              | $f \in \{par, alt\}$                           | $f(x,y) \approx f(y,x)$                                  |

| Idempotence                | alt                                            | alt(x,x) pprox x                                         |

| Unit element $\varnothing$ | $f \in \{seq, par\}$                           | $f(x,\varnothing) \approx x, f(\varnothing,x) \approx x$ |

| Ø-fixpoint                 | loop                                           | $loop(\emptyset) \approx \emptyset$                      |

Table. Basic set E of algebraic equations of the Interaction Language

#### Interaction composition

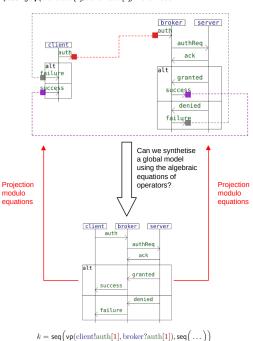

Model composition involves synthesising a new model by gluing complementary actions those linked by a shared gate into message passings (vp), while preserving the scheduling information of the original models. A valid composition must project [2] back to the initial models from which it was constructed.

In our example, the emission and reception of auth are composed into the message passing  $\mathbf{vp}(\text{client!auth}[1],\text{lroker?auth}[1])$  in the model k.

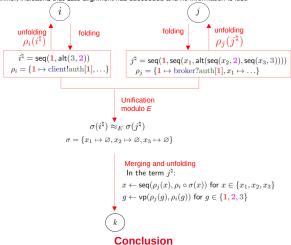

#### Composition through generalisation

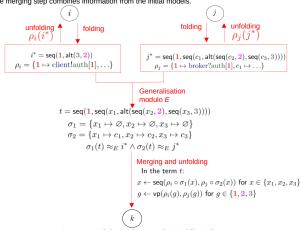

The first step is **model folding**, which hides subterms that contain no actions relevant to the composition inside fresh constants, and replaces actions with their associated gates. The resulting folded terms are significantly simpler and are then generalised modulo E [3]. The **desired generaliser must include all relevant gates**, indicating successful alignment of complementary actions. Such a generaliser is said to be **well-formed**. Finally, the merging step combines information from the initial models.

#### Composition through unification

The first step is model folding, where actions are replaced by their associated gates. Unlike the previous approach, irrelevant subterms are hidden using fresh variables. The second step is unification modulo E [4]. The desired unifier maps variables to subterms that contain no gates, and ensures that applying it to one term yields a structure containing exactly all the variables of the other. These two conditions define what we call a well-formed unifier, indicating that gate alignment has succeeded and no information is lost.

We have explored two methods for composing interactions using algebraic equations. These approaches are not interchangeable, as there are cases where a well-formed generaliser exists while no well-formed unifier can be found. We are therefore interested in delineating the scope of each method and their respective ability to decide when composition is possible. Future work will focus on formalising correctness guarantees and investigating algorithmic aspects.

[1] Mahe, Erwan. An Operational Semantics of Interactions for Verifying Partially Observed Executions of Distributed Systems. Phdthesis, Université Paris-Saclay, 2021.

[2] Julien Lange and Emilio Tuosto. Synthesising choreographies from local session types In 23rd international conference on Concurrency Theory (CONCUR'12), 2012.

[3] M. Alpuente, S. Escobar, J. Meseguer, and J. Sapina. Order-sorted equational generalization algorithm revisited. Annals of Mathematics and Artificial Intelligence, 2022.

[4] S. Escobar, J. Meseguer, and R. Sasse. Variant Narrowing and Equational Unification.

Electronic Notes in Theoretical Computer Science, 2009.

# Deductive Verification of Synchronous Reactive Programs

Frédéric Dabrowski Térence Clastres Journées du GDR-GPL, Juin 2025

# Description

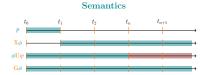

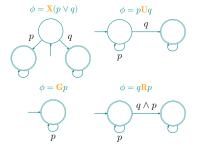

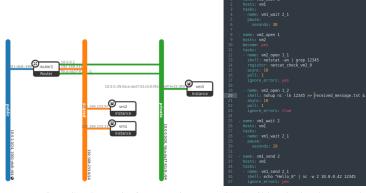

Ce poster décrit un travail en cours sur le développement d'une technique de vérification de propriétés de programmes réactifs. Ces programmes s'exécutant en continu afin de réagir à leur environnement, leur spécification doit décrire leur comportement dans le temps sous forme de propriétés temporelles.

Le standard pour la vérification de ces propriétés est le model-checking: on considère des modèles qui représentent de manière abstraite le comportement des programmes. Ces modèles sont des systèmes de transitions finis. Comme la spécification caractérise l'ensemble des comportements corrects, le but est de vérifier de manière automatique que les comportements du programme sont inclus dans ceux de la spécification. Cependant, cette technique comporte deux inconvénients: Premièrement, il faut s'assurer que le modèle est bien une abstraction (sûr-approximation) du programme. Deuxièmement, les programmes complexes amènent rapidement à une explosion combinatoire ayant pour conséquence des durées de vérification déraisonnables. Après 30 ans d'existence, de nombreux travaux ont eu pour but de combattre ces faiblesses (model-checking symbolique, raffinement de modèle, parallélisme, heuristiques de recherche...). Cependant, à partir du moment où les programmes manipulent des domaines infinis, il n'est possible que de vérifier des sous-domaines finis.

Contrairement au model-checking, la vérification déductive fait le lien direct entre la syntaxe du programme, sa sémantique et sa spécification. Elle nécessite de prouver un ensemble de théorèmes afin de garantir la conformité du programme. De plus, alors que le model-checking peut être vu comme une façon de faire du test, généralement incomplet, la preuve permet de mener un raisonnement sur l'entièreté du domaine, qu'il soit fini ou infini. Il n'est néanmoins pas possible en général d'espérer trouver automatiquement une preuve. Aussi, la vérification déductive a principalement été étudiée dans le cadre de programmes qui terminent, c'est-à-dire pour lesquels on ne s'intéresse pas au comportement dans le temps.

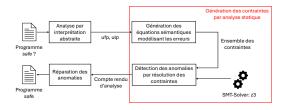

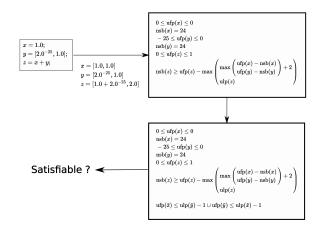

Avec notre approche, nous désirons adapter la vérification déductive aux programmes réactifs : à partir d'un programme annoté, un ensemble de théorèmes sont générés. Ces théorèmes peuvent être prouvés automatiquement où par l'utilisateur, l'intention étant de ne faire intervenir celui-ci que pour des théorèmes non triviaux nécessitant une connaissance profonde du programme à vérifier.

# DEDUCTIVE VERIFICATION OF SYNCHRONOUS REACTIVE PROGRAMS

# Térence Clastres, Frédéric Dabrowski Université d'Orléans, INSA CVL, LIFO, UR 4022, Orléans, France

## **Deductive Verification**

- Formal method to verify the functional correctness of programs